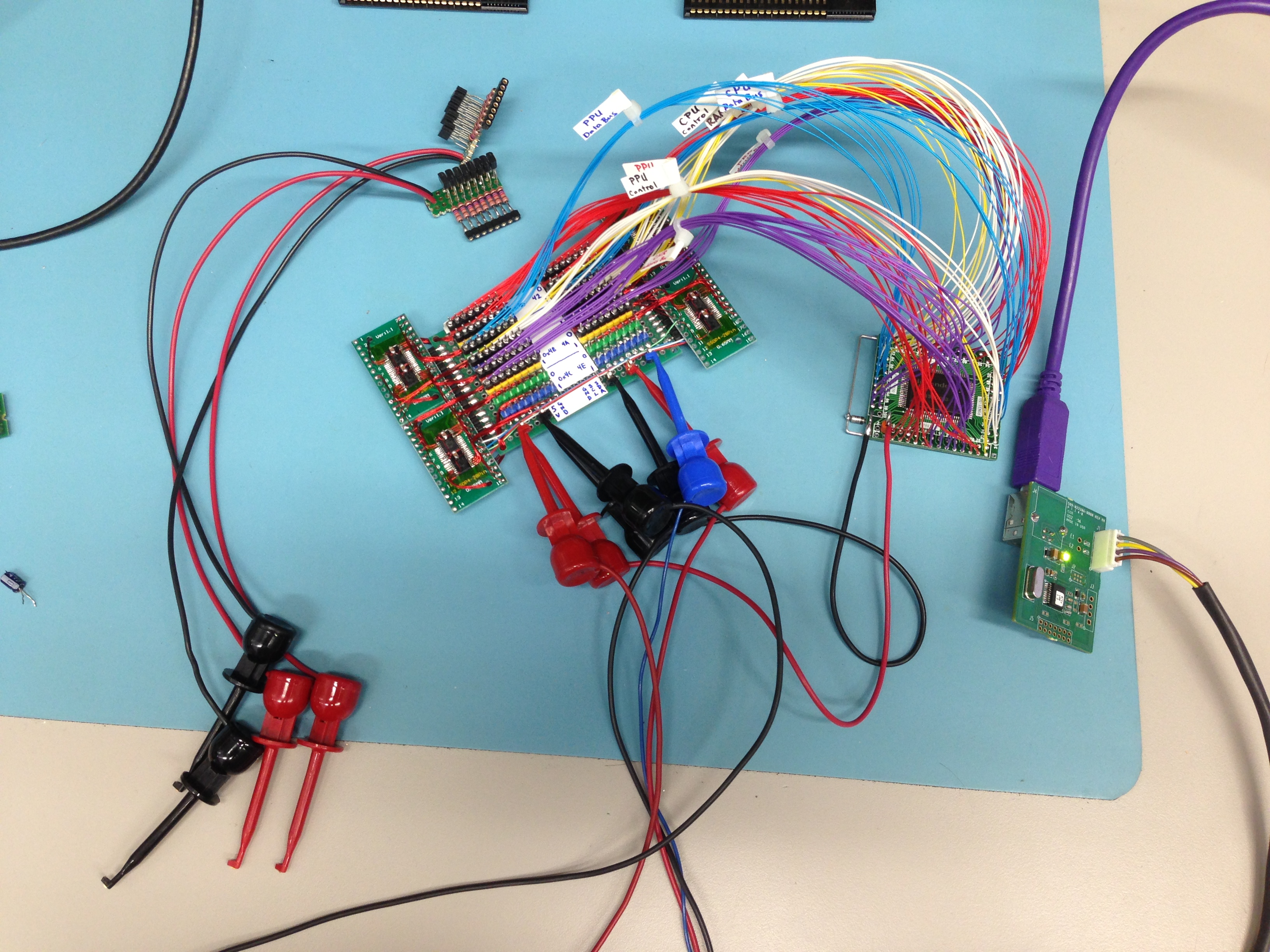

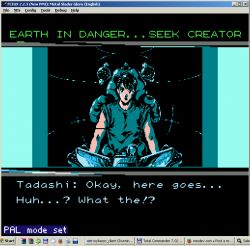

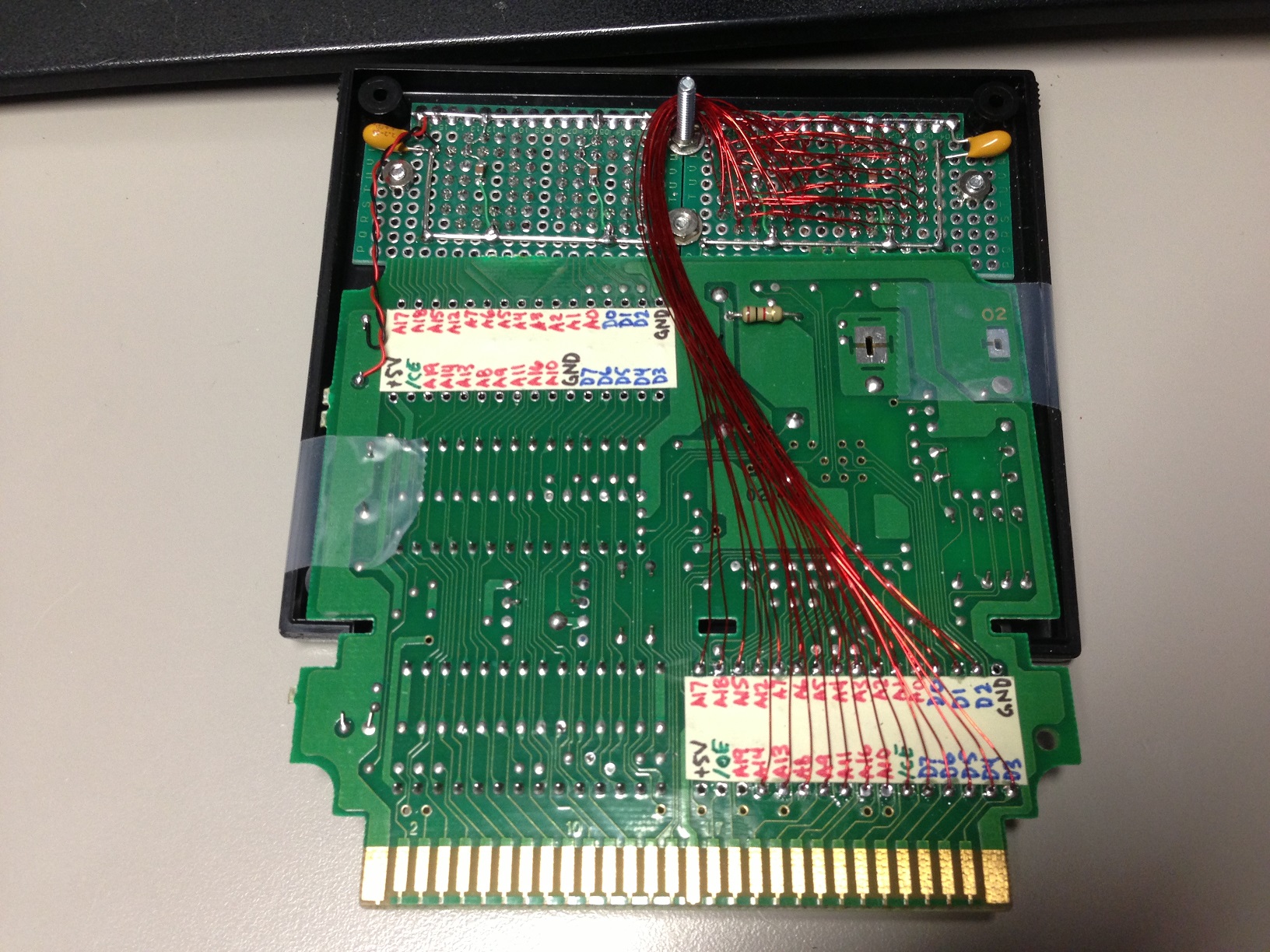

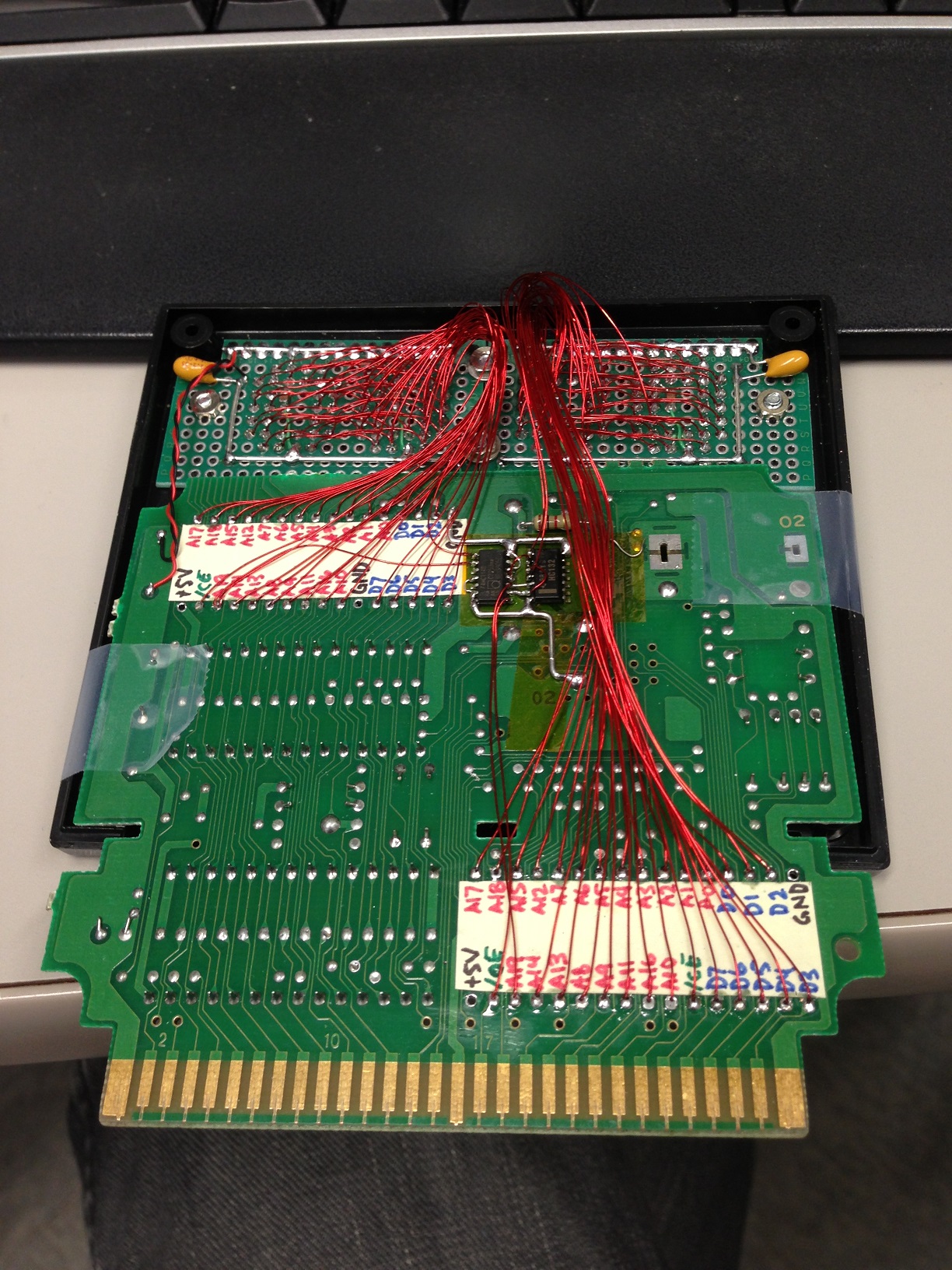

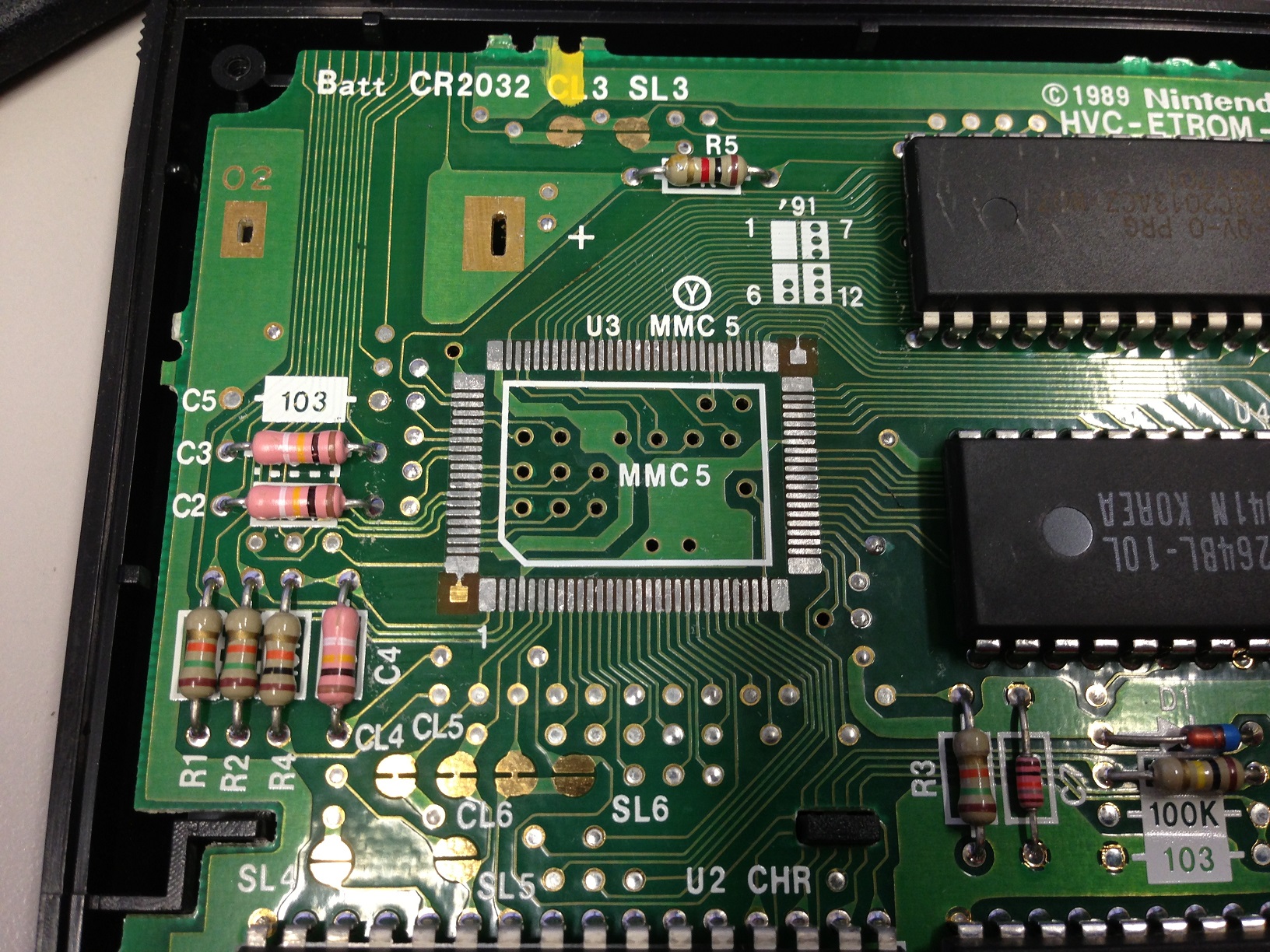

As a lunchtime and after-work activity, I have slowly built and finally completed a setup to hack the MMC5.

- 8x 16-bit TTL-compatible I2C I/O expanders (totaling 128 bits I/O)

- USB to I2C adapter

- Donor MMC5A chip from 'Just Breed', removed successfully

- 0.65mm pitch QFP-100 20x30 breakout board, MMC5A mounted on it successfully

- All connections from I/O expanders to MMC5 complete (except audio)

- Preliminary C# GUI on computer to create automated tests, to let it run overnight, etc.

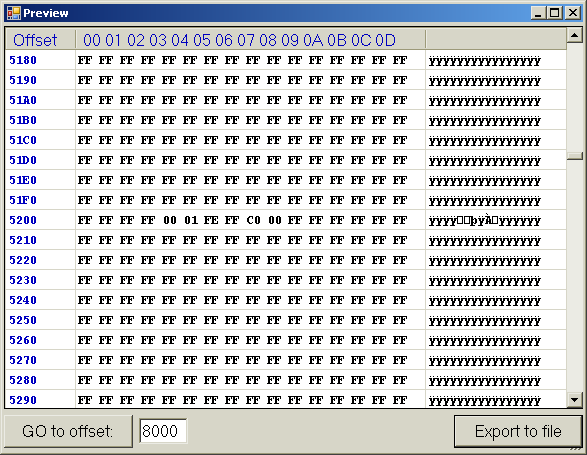

Attachment:

File comment: MMC5 hack rat's nest

IMG_1541.JPG [ 2.4 MiB | Viewed 22174 times ]

IMG_1541.JPG [ 2.4 MiB | Viewed 22174 times ]

I put a series 100 ohm on each pin in case I goof up and hook 2 outputs together, hopefully saving it if that happens. I have a current-limited voltage source I plan to use as well. The I/O expanders default to input when power is applied and have a 100k internal pull-up when set as input. I created controllable 10k pull-downs for the CPU and PPU data busses so I can test whether the MMC5 is driving the bus or is in open bus / high impedance state.

The first auto-test that I want to create is to try reading from all possible CPU addresses, recording whether the MMC5 is open bus or reporting a value. If it is a value, recording the value. This will tell us each and every address to which the MMC5A responds, and nail down that aspect for the memory map. I will get this test working first, then we can think about what to do next. I would like to start reading and writing to PRG-RAM and watching the unknown lines in the not-too-distant future. I am pretty sure we will be OK on noise and wire length because I will be controlling the M2 line manually with the I/O expanders. This will definitely be a very slow-mo test process.

My goal is to work on the GUI this weekend and see if I can get some sort of test running. Will report progress!

Ben Boldt wrote:

The first auto-test that I want to create is to try reading from all possible CPU addresses, recording whether the MMC5 is open bus or reporting a value. If it is a value, recording the value. This will tell us each and every address to which the MMC5A responds, and nail down that aspect for the memory map.

I believe this test was done many years ago using a CopyNES, and it revealed that the only readable addresses were $5010, $5015, $5204-$5206, and $5C00-$5FFF

if ExRAM is in "ordinary RAM" mode (i.e. last value written to $5104 was 2 or 3).

Still, it never hurts to recheck these sorts of things, and it'll still be useful in confirming that your testing rig is working correctly.

Here is what I found today:

With these settings:

CPU R/W = 1

/ROMSEL = 1

M2 = 1

The MMC5A drives the CPU data bus when reading from these addresses:

$5010: $01

$5015: $00

$5204: $00

$5205: $01

$5206: $FE

$5208: $C0

$5209: $00

$5C00 - 5FFF: all $00

All reads result in open bus when /ROMSEL = 0.

When M2 = 1, MMC5 register data appears on CPU data bus asynchronously. For the entire test, I stuck M2 = 1, no toggling. However, running my same test with M2 = 0, the data bus is always open bus. I would suspect that the data bus updates when M2 = 1 and then latches whatever it had when M2 = 0.

Interesting to consider what the heck $5208 and $5209 are doing. This comes right after the 8x8->16 multiplier.

Ben Boldt wrote:

However, running my same test with M2 = 0, the data bus is always open bus.

Isn't that what you expected? What were you testing for?

Quote:

I would suspect that the data bus updates when M2 = 1 and then latches whatever it had when M2 = 0.

I fully expect it's the "normal" transparent latch interface we've seen through the design on the 2A03 / 2C02...

I want you guys to know that I am going to be pretty new to a lot of this -- I have done a few things where I have changed ROMs in cartridges, but I have never gone deep like this. Never before have I had a need to think about which edge of the clock the data bus is updated, etc, so this is going to be pretty awesome for me, and maybe a little elementary for some of you veterans. I am good at making fancy tools and stuff to help me explore and learn, that is my forte. I would like your ideas to help design more useful tests. I do have all pins controllable with this setup, except for audio.

Anyway, I think that this test has proven that my tools are running pretty well. I might try messing with the multiplier next, seeing how many clocks it requires (if any) to get the correct result. Then I might poke at 5208/5209. Does anyone have any idea what these 2 registers might do? Hopefully it is a divide, that would be awesome.

Ben Boldt wrote:

I want you guys to know that I am going to be pretty new to a lot of this

Ah, ok. That makes sense!

My best guess is that $5208 and $5209 expose some portion of the internal multiplier state.

The only real thing left to be done with the MMC5 audio is characterize its amplifier. The last time I hooked up this copy of Laser Invasion to anything I apparently only got as far as measuring its slew rate: the really quite slow 0.42V/µs. But I never got as far measuring a transfer curve ... ok, fine, I should stop putting that off...

I hooked up a variety of resistors and capacitors from the calibration output out of my 'scope, trying to make something sufficiently similar to a function generator to generate a voltage sweep. Unfortunately, my test conditions are lousy enough that I'm only seeing bad behaviors due to recovering from hitting the supply rails: gains in the linear region vary from 50 to 500, and there's a DC difference between recovering from positive rail and negative rail.

I created a new test today that gives every possible combination of inputs to the multiplier and reads its output, and also $5208 and $5209.

The test runs like this:

for( int i = 0; i < 65536, i++ )

{

Drive M2 high

Drive CPU R/W low (write mode)

Drive CPU address bus to $5205

Drive bits 0-7 of i onto data bus

(Record bits 0-7 to spreadsheet)

Drive M2 Low (falling edge of the clock registering the data into the multiplier)

Drive M2 back high

Drive CPU address bus to $5206

Drive bits 8-15 of i onto data bus

(Record bits 8-15 to spreadsheet)

Drive M2 Low (falling edge of the clock registering the data into the multiplier)

Stop driving CPU data bus - make it an input on my analyzer.

Drive M2 back high

Drive CPU R/W high

Read from $5205, 5206, 5208, 5209, recording each to spreadsheet.

}

After an hour of so, the test was complete and I had my spreadsheet. Then I added additional columns to check the results and see if there was any effect on $5208 and $5209. I found that the multiplier provided the correct answer with no extra M2 cycles for all 65536 combinations, and there was no change ever witnessed on $5208 and $5209. It seems they are not related to the result of the multiplier.

I attached the spreadsheet. I had to zip it to fit under 4 MiB attachment limit.

Do you know how much time happens between when you drive M2 high and M2 low?

The multiplier in the MMC5 could plausibly not be clocked but instead just asynchronous. Although... we don't say anything about required delays on the MMC5 wiki page so maybe it really is just that fast.

Ben Boldt wrote:

Drive M2 Low (falling edge of the clock registering the data into the multiplier)

Drive M2 back high

Drive CPU address bus to $5206

When the actual 6502/2A03 writes, the address bus and data bus are stable, then M2 goes high and then low. Evidently things work otherwise, but.

Given the asynchronous nature you've already observed, you might be able to get away without toggling M2 at all, much like how asynchronous writes to a SRAM work: just

A<- $5205

R/W low

M2 high

D<- mutlipland

A<-$5206

D<- multiplier

R/W high

upper byte of result ->D

A<-$5205

lower byte of result ->D

Each group of 8-bits in the analyzer takes me approx. 15 msec to read or write. So basically forever compared to a real NES. I guess we don't know if the MMC5 has an internal clock. I know that it isn't uncommon for microcontrollers to have a 1-cycle multiply. I will see about writing a test for multiply without M2 as you prescribed.

I tried writing a few values to $5207, 5208, and 5209, including all 00 00 00, then FF FF FF, and then xx 00 00 where xx repeated attempts 00-ff. All of these fed back the same C0 00 response from $5208/5209. So no clues yet figuring out what that might be.

Ben Boldt wrote:

I will see about writing a test for multiply without M2 as you prescribed.

Only if you want. I don't think it'll establish anything new; I'm just pointing out how asynchronous interfaces work: changing the address is as good as ending the active condition (M2 falling).

Quote:

So no clues yet figuring out what that might be.

Other possibilities would be for factory verification of things; perhaps it reflects banking status. Does anything change in those two registers when the PPU address changes?

*Yes, I can confirm, on my Just Breed it gives similar read results on powerup:

*Maybe this C0 at $5208 is some kind of version (signature), or it returns some what mode MMC5 is is (SL/CL)

*Multiplicator is asynchronous and gives result immediatelly (not like in Mapper 90 when you have to wait 8 cycles for shifting 8 bits of multiplicands internally)

*MMC5 must have some kind of internal clock OR reset detector, because if you stop cycling M2 at 1.7MHz, it returns to power-up state (EXRAM and RAMs becomes write-protected, same applies to the read-back of register below)

*If you write something nonzero to $5209, interrupt is immediatelly asserted. First read of $5209 returns $80 (and interrupt is deasserted), next ones return $00. It is completely independent from $5204 (disabling interrupts through $5204 does not make any effect, also reading $5204 does not report IRQ pending when IRQ is asserted b $5209)

*If there is battery, MMC5's EXRAM content is backed up.

* If you try to read back $5c00-$5fff on powerup, it returns zeros. If you switch EXRAM mode to 0/1 - it returns FFs, if you switch it to 2/3 - it returns its content. So the power up state is something different.

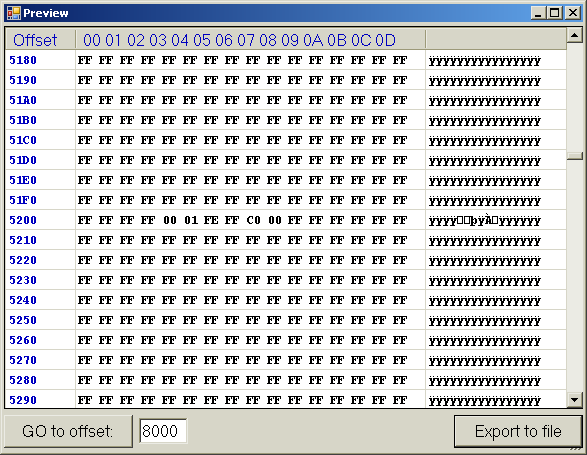

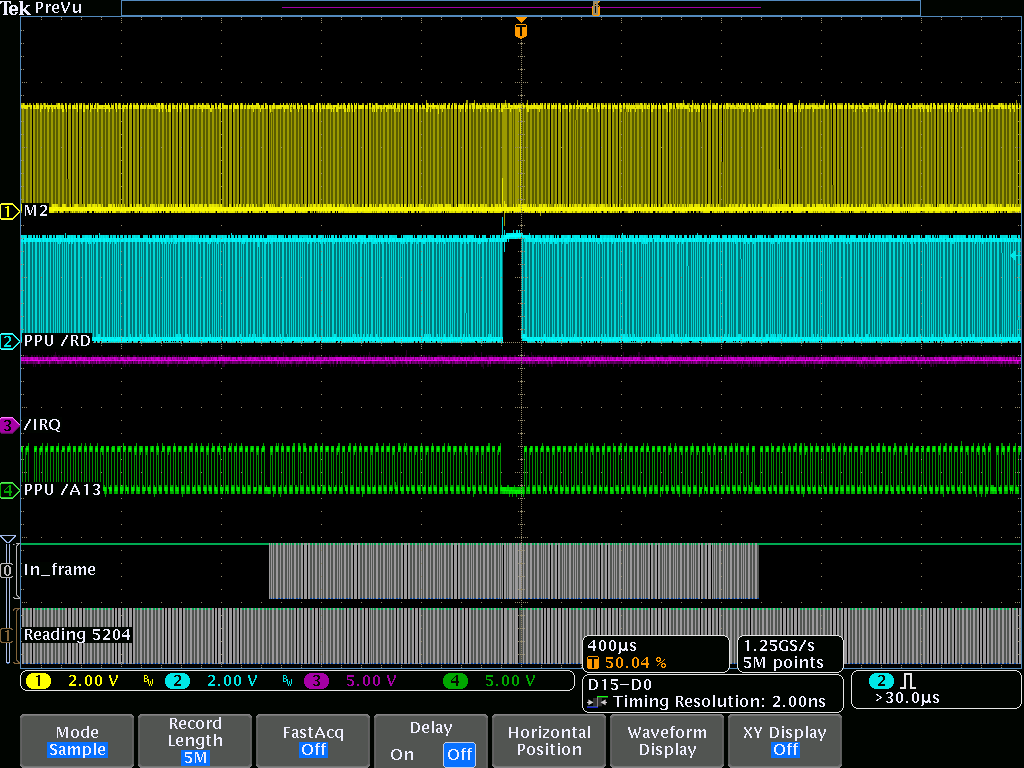

New test, reading from all PPU addresses this time. I am VERY unfamiliar with the PPU, so please help me interpret the results.

CPU R/W = driven to 1

/ROMSEL = driven to 0

M2 = driven to 1

PPU /WR = driven to 1

PPU /RD = driven to 0

for (int i = 0; i < 16384; i++)

{

- Set PPU data bus to have pull-up (i.e. high-z shows up as $FF)

- Drive PPU address bus to i, with bit 13 of i inverted before fed to PPU /A13

- Read and record PPU data bus to spreadsheet.

- Set PPU data bus to have pull-down (i.e. high-z = $00.)

- Read and record PPU data bus again.

- Read and record various control bits.

}

During this entire test, I observed:

- all unknown pins (29, 30, 73, 75, 81, 82, 92, 93) stayed high.

- CIRAM /CE stayed high

- CIRAM A10 stayed high

But please someone explain this to me:

- MMC5 drove the PPU data bus to $FF for all address in the range $2000 to $2FFF. (i.e. the pull downs were overcome, the bus stayed high)

- PPU data bus was high-z for $0000 to $1FFF and $3000 to $3FFF

Quote:

But please someone explain this to me:

- MMC5 drove the PPU data bus to $FF for all address in the range $2000 to $2FFF. (i.e. the pull downs were overcome, the bus stayed high)

Power up state for many MMC5 registers is $FFs (if $5105 = $FF, $5106=$FF, $5107=$FF), so all four nametables are in fill-mode byte mode which returns $FF for all $2000-$2fff.

Thanks krzysiobal, I'm glad it makes sense.

My intention with this test was to answer your question lidnariq:

Quote:

Does anything change in those two registers when the PPU address changes?

And of course I forgot to read those registers. Will do so tomorrow.

Ben Boldt wrote:

- all unknown pins (29, 30, 73, 75, 81, 82, 92, 93) stayed high.

So much for my guess that pin 29 or 30 could possibly be

PPUA13 OR /PPURD...

Update:

None of the readable registers changed value reported when reading from all PPU address. I elected to skip reading the multiplier registers for this test.

All remained with these values:

$5010: $01 PCM Mode/IRQ (bit 0 = 1: read mode, bit 7 = 0: PCM IRQ not enabled)

$5015: $00 APU Status

$5204: $40 IRQ Status ($40 means it thinks I'm "in frame" for this test, and no IRQ pending.)

$5208: $C0 ? (unknown)

$5209: $00 ? IRQ-related per krzysiobal

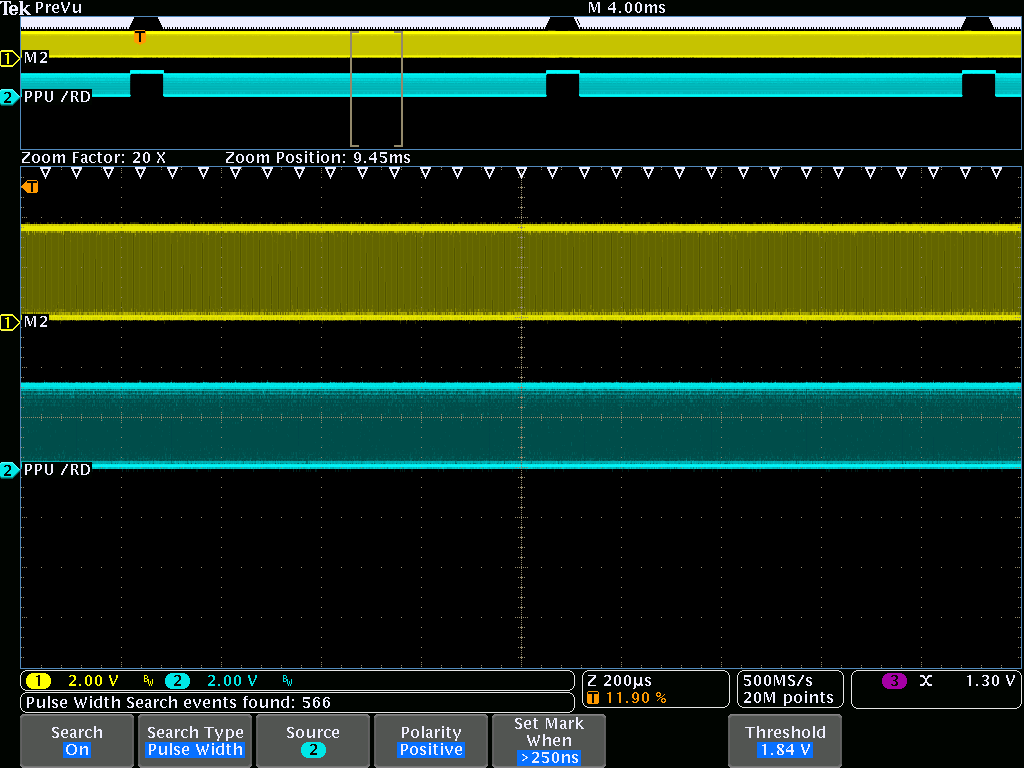

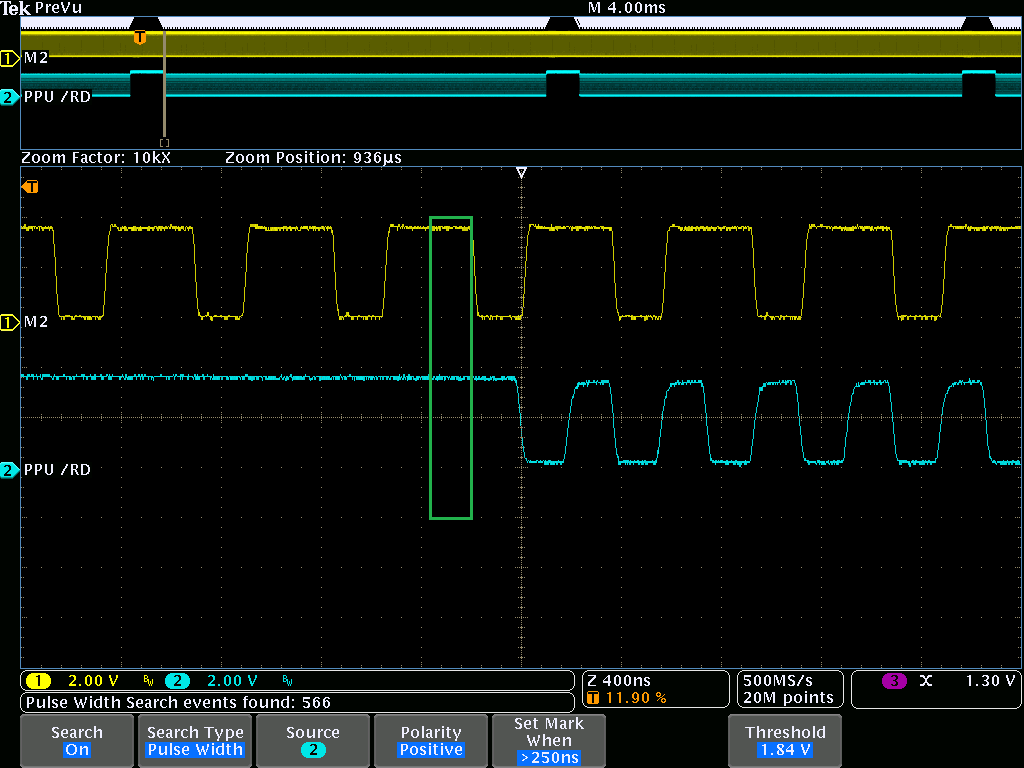

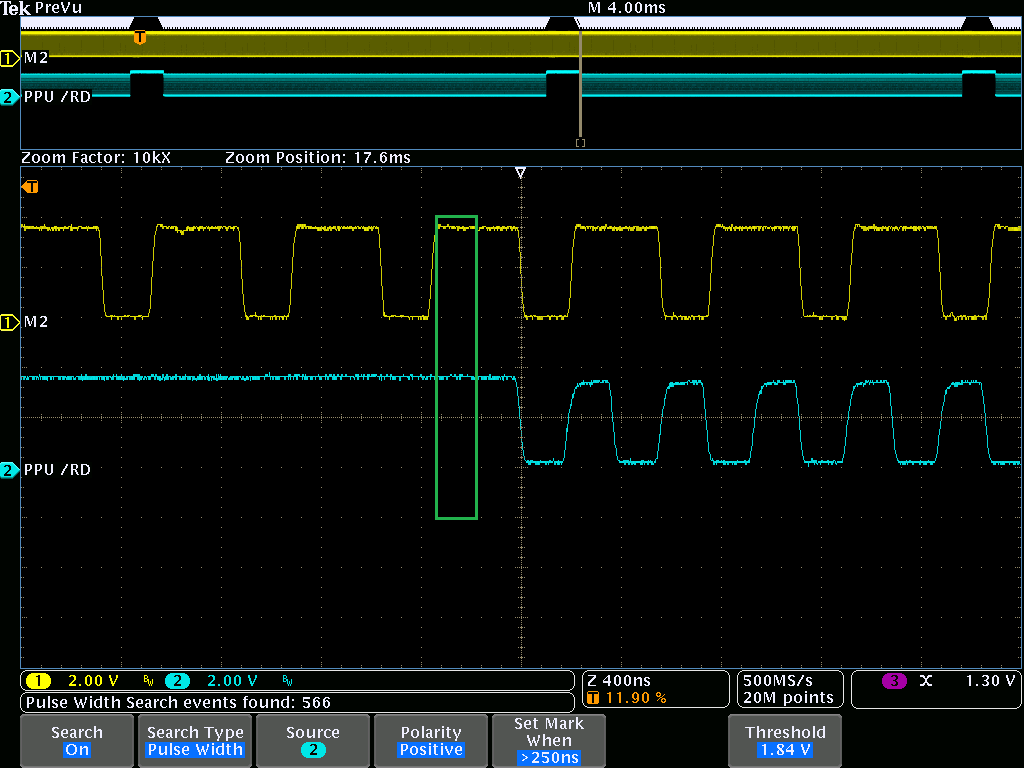

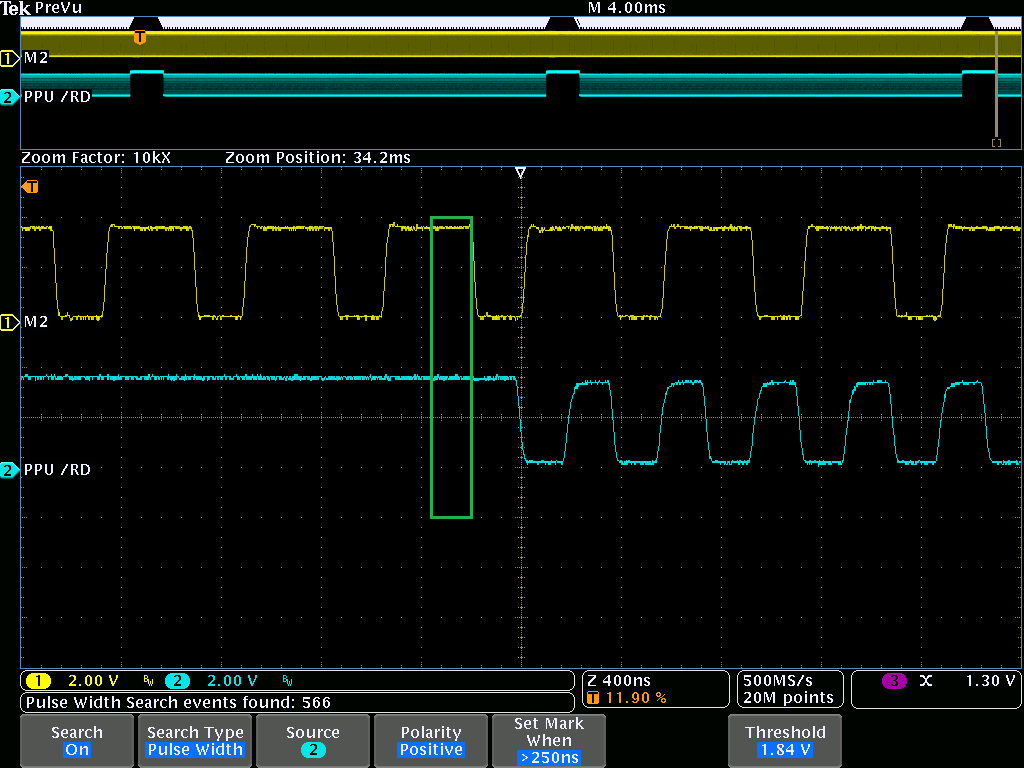

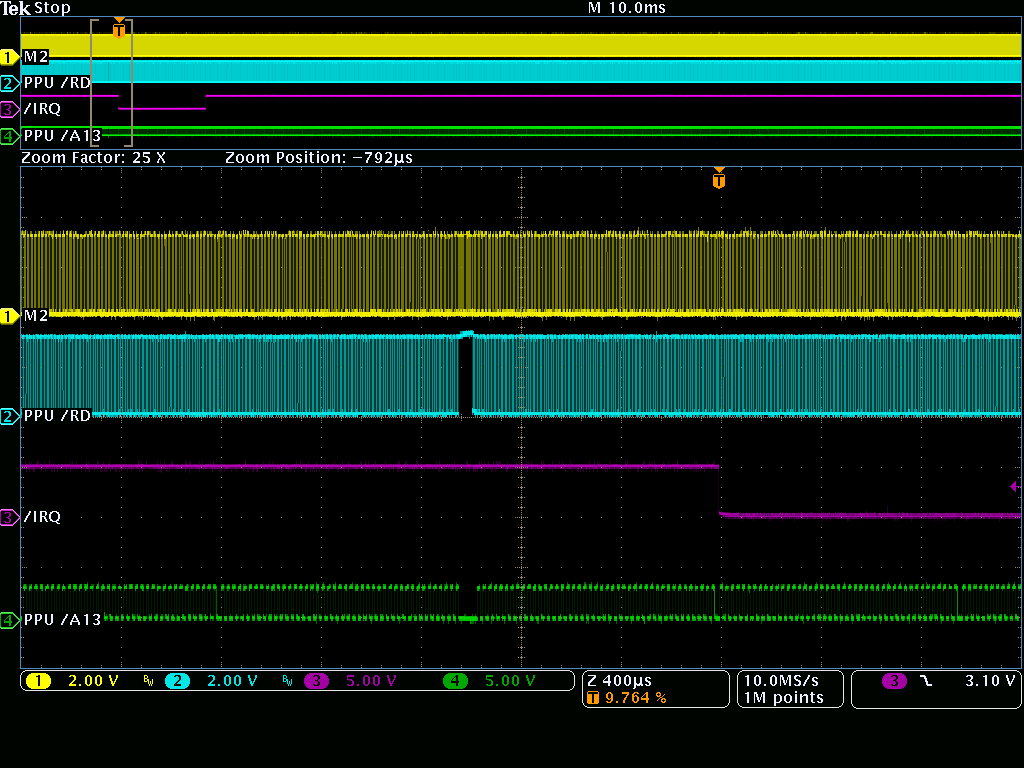

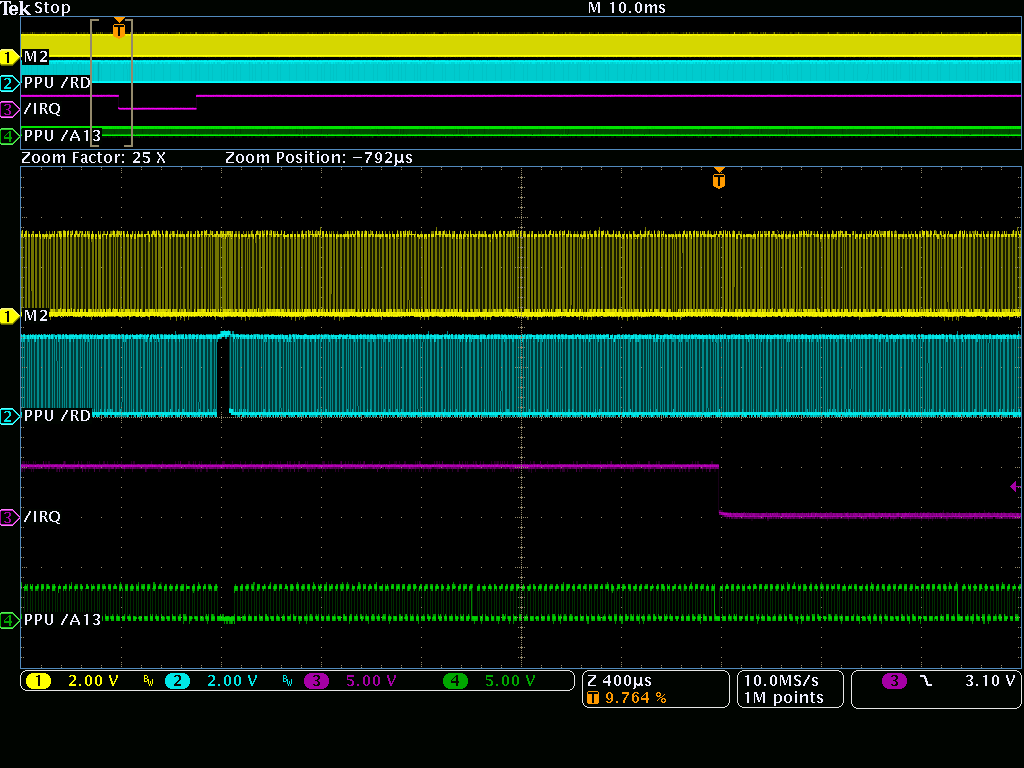

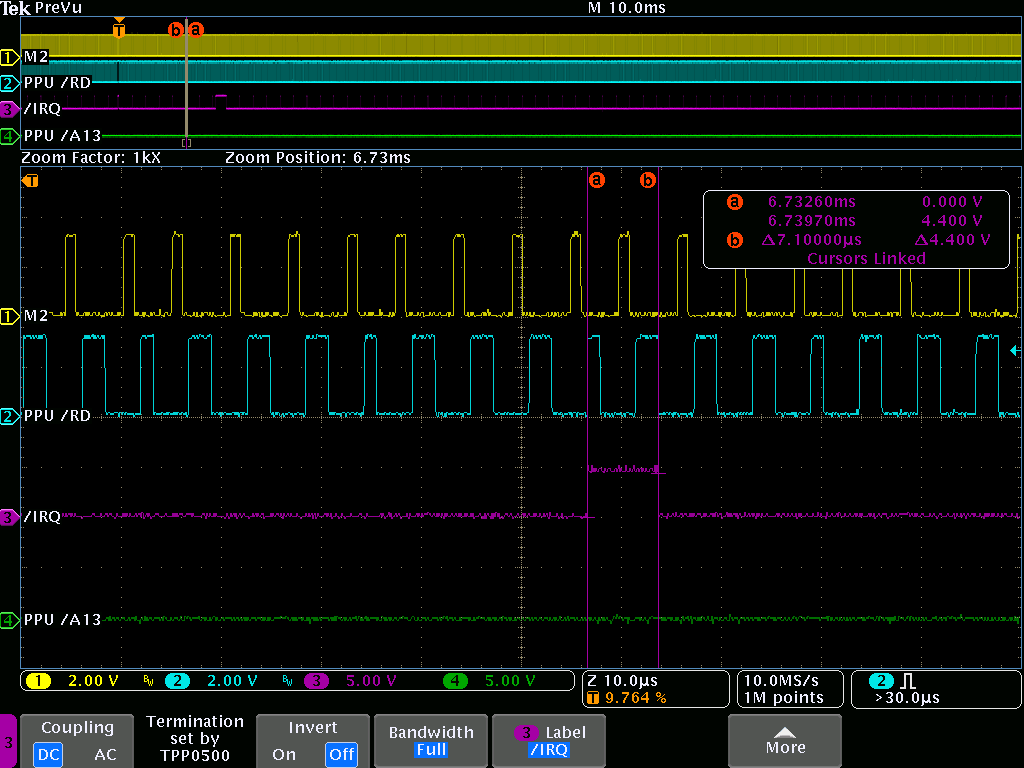

I looked at Register $5204 (IRQ Status) bit 6 ("In Frame").

- At power-up of the MMC5, this status bit = 0.

- The bit goes high whenever PPU /RD goes low.

- The bit stays latched high even when PPU /RD goes back high

- PPU /WR seems to have no effect on this bit, whether the bit = 0 or 1.

- I tried all sequences of /RD and /WR and nothing would cause the status bit to return to 0.

- I tried toggling /RD 1000 times and the status bit still stayed 1 the whole time.

- Also tried toggling /WR 1000 times, no luck.

Does anyone know how "in frame" is cleared? I think that understanding this might be a good step towards understanding how the scanline counter works.

Quote:

Does anyone know how "in frame" is cleared? I think that understanding this might be a good step towards understanding how the scanline counter works.

Check what I wrote at end of this topic:

https://forums.nesdev.com/viewtopic.php ... 89#p209443

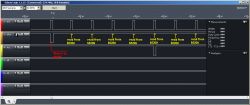

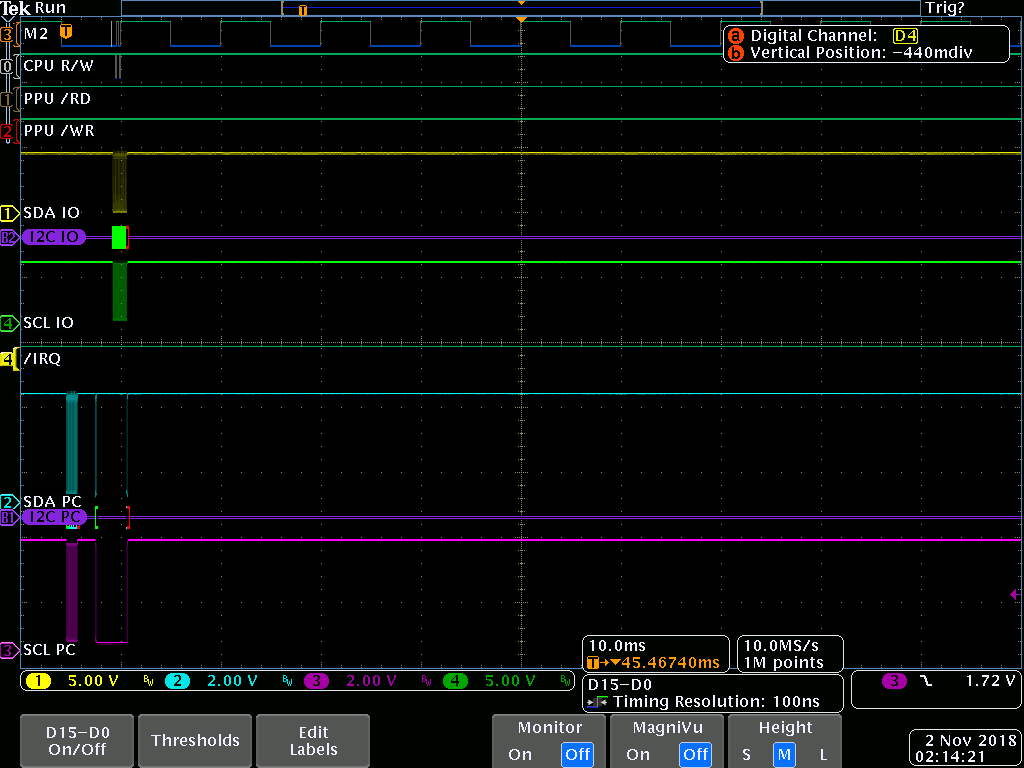

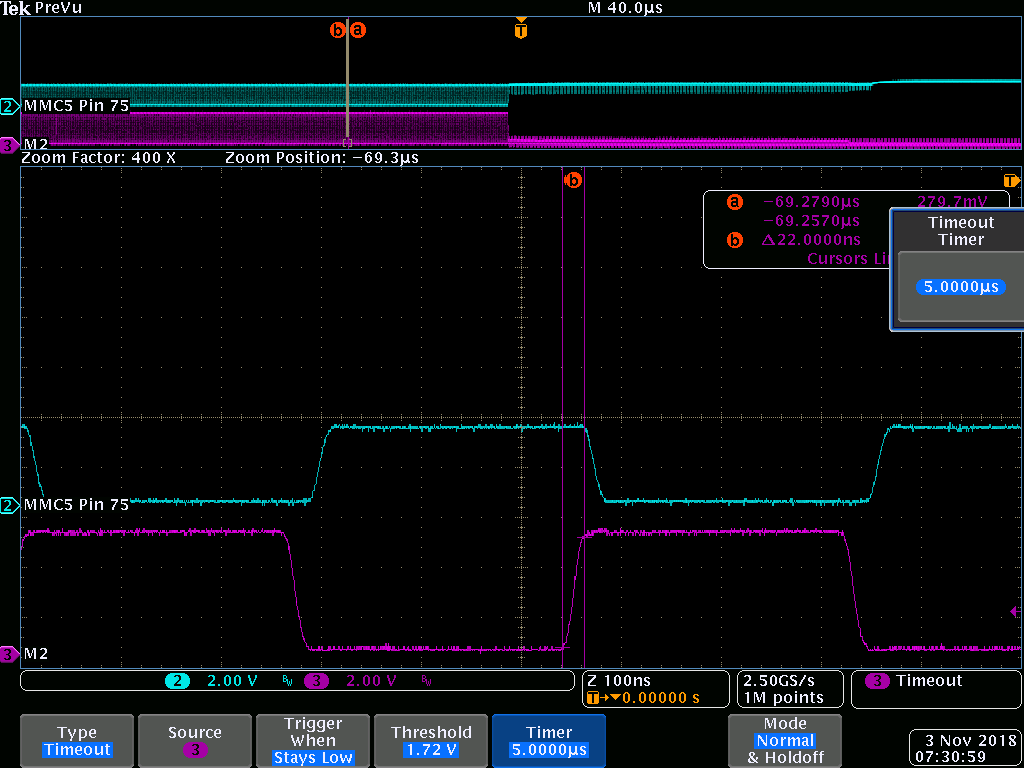

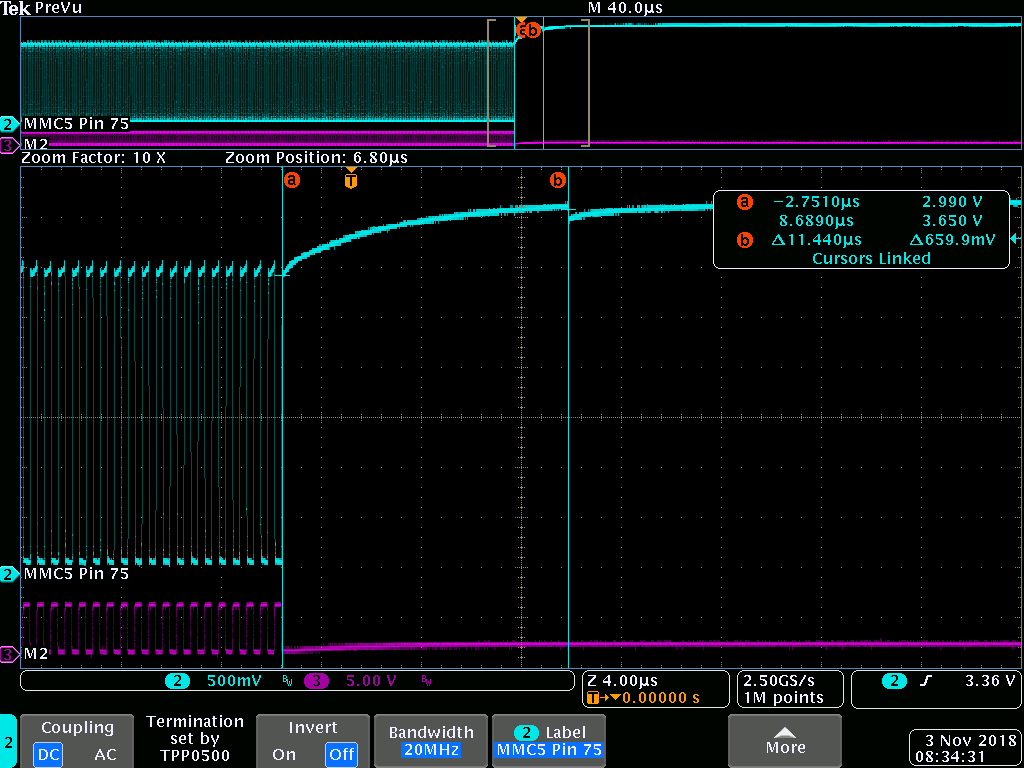

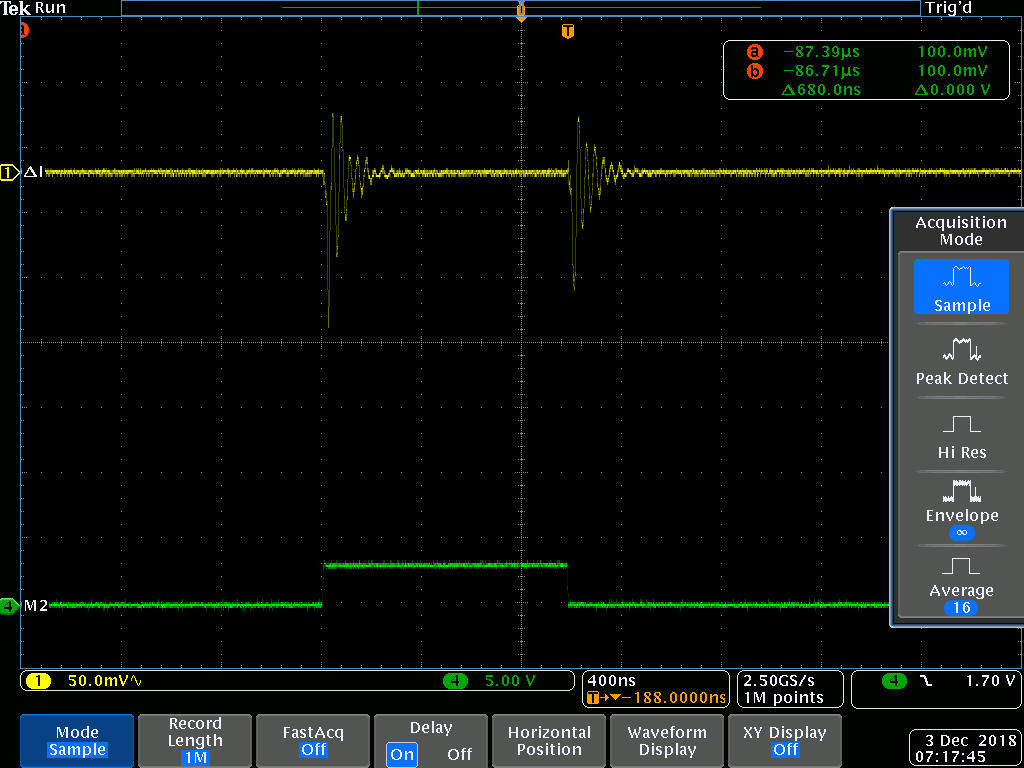

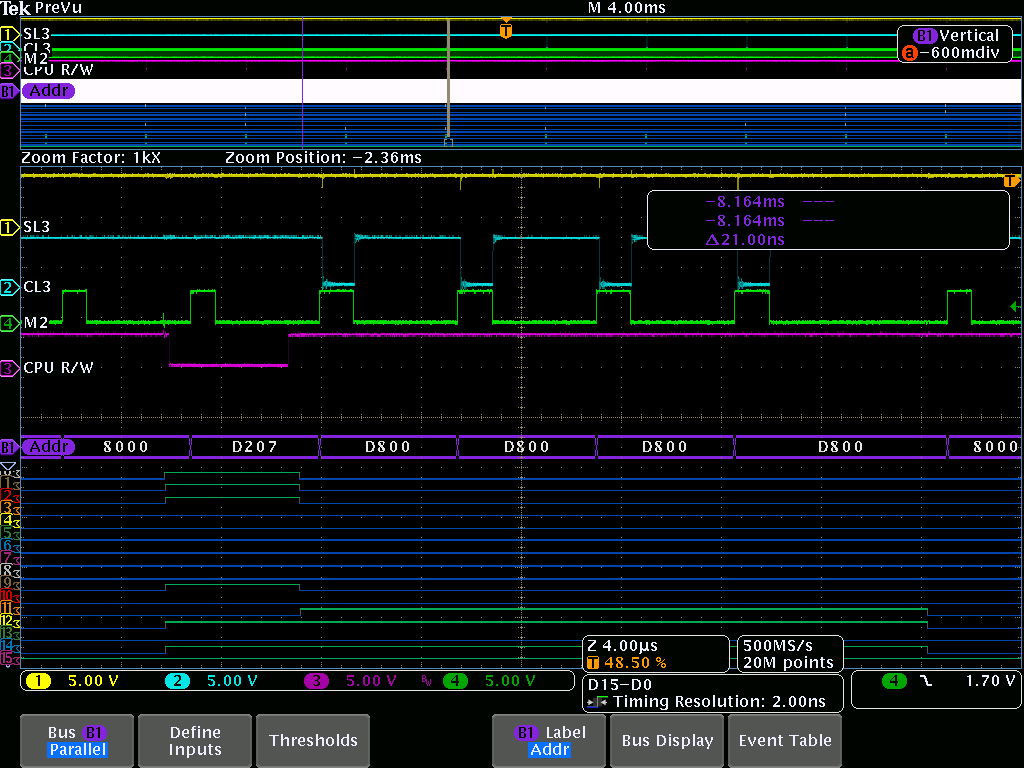

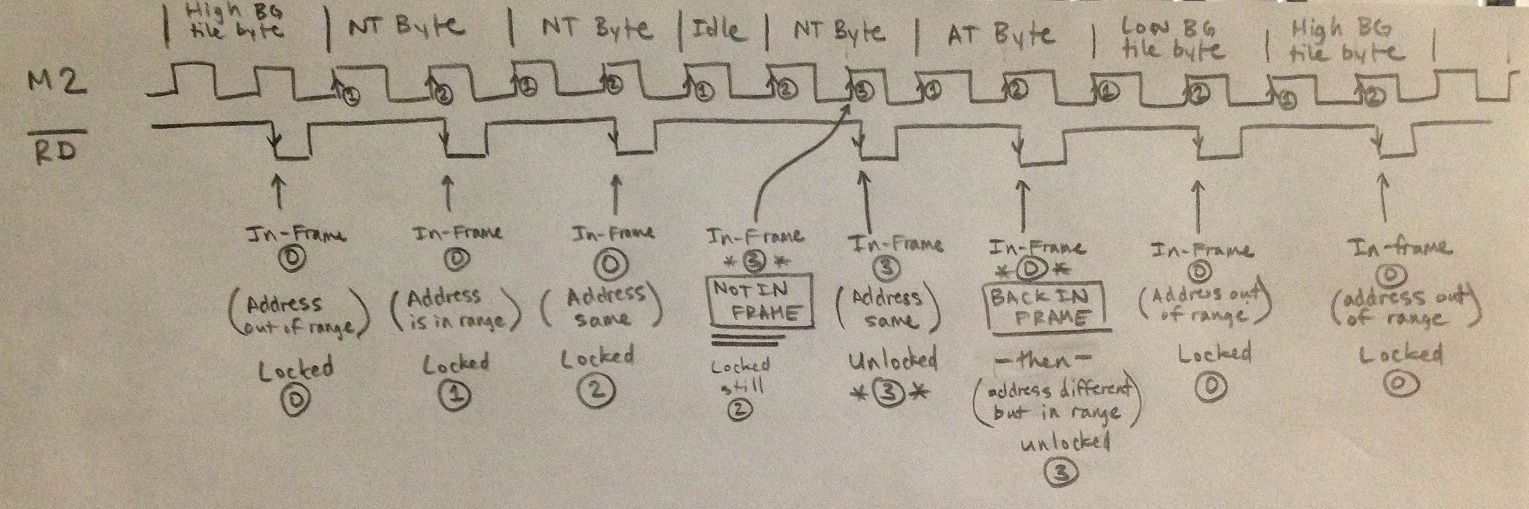

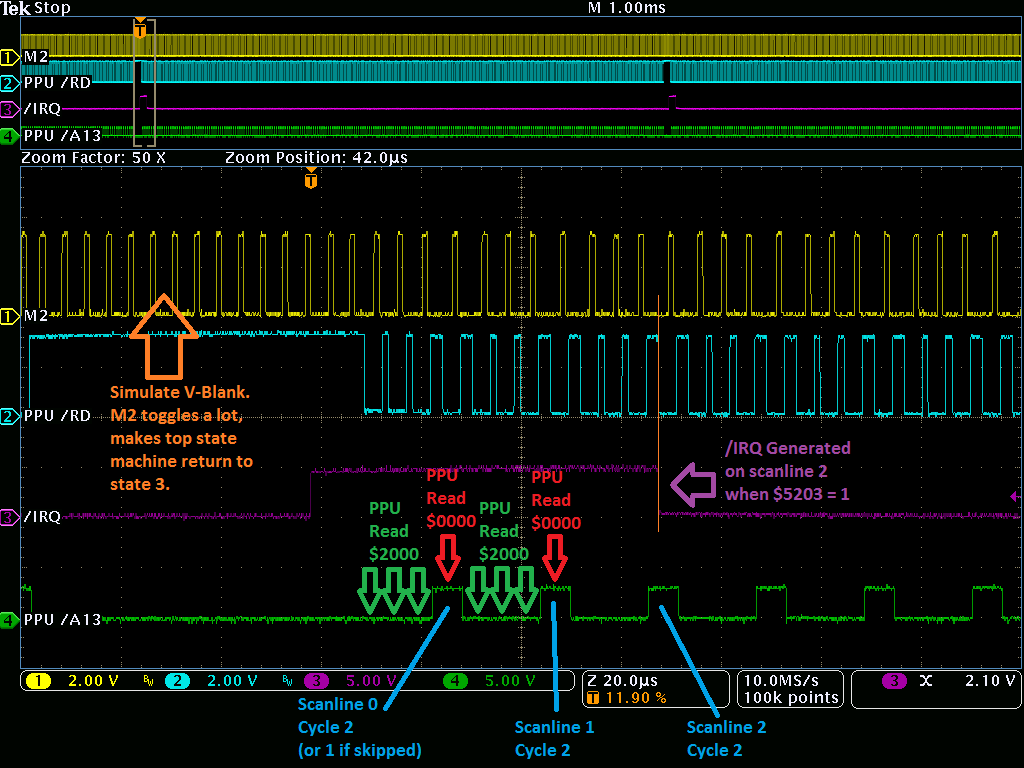

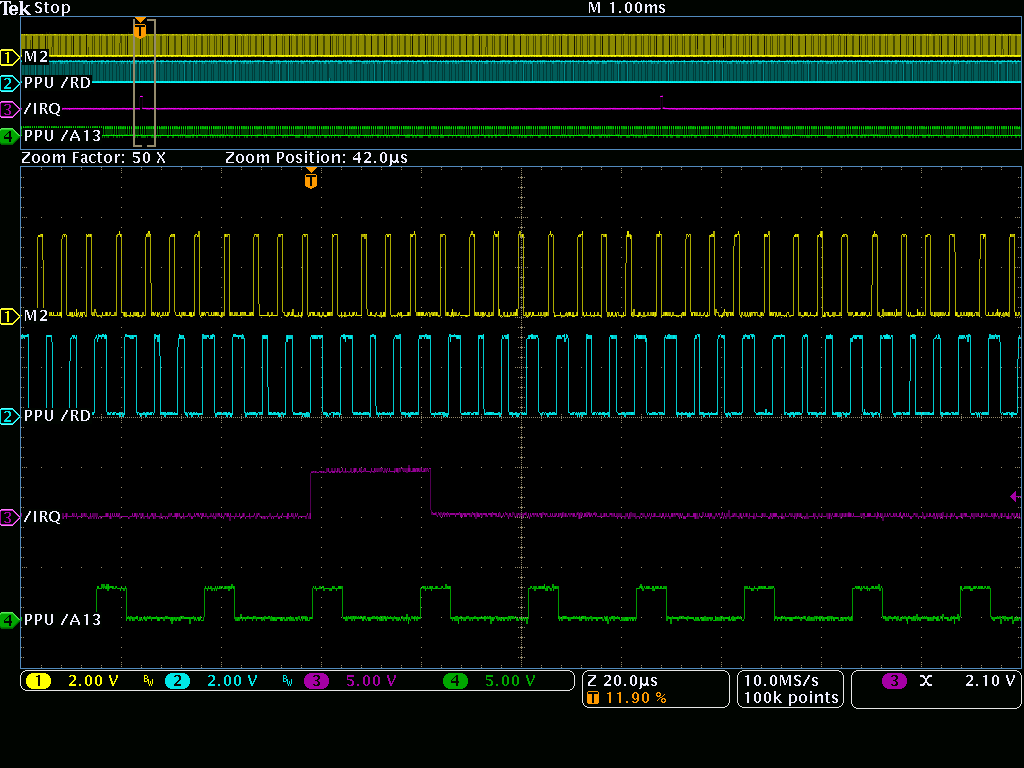

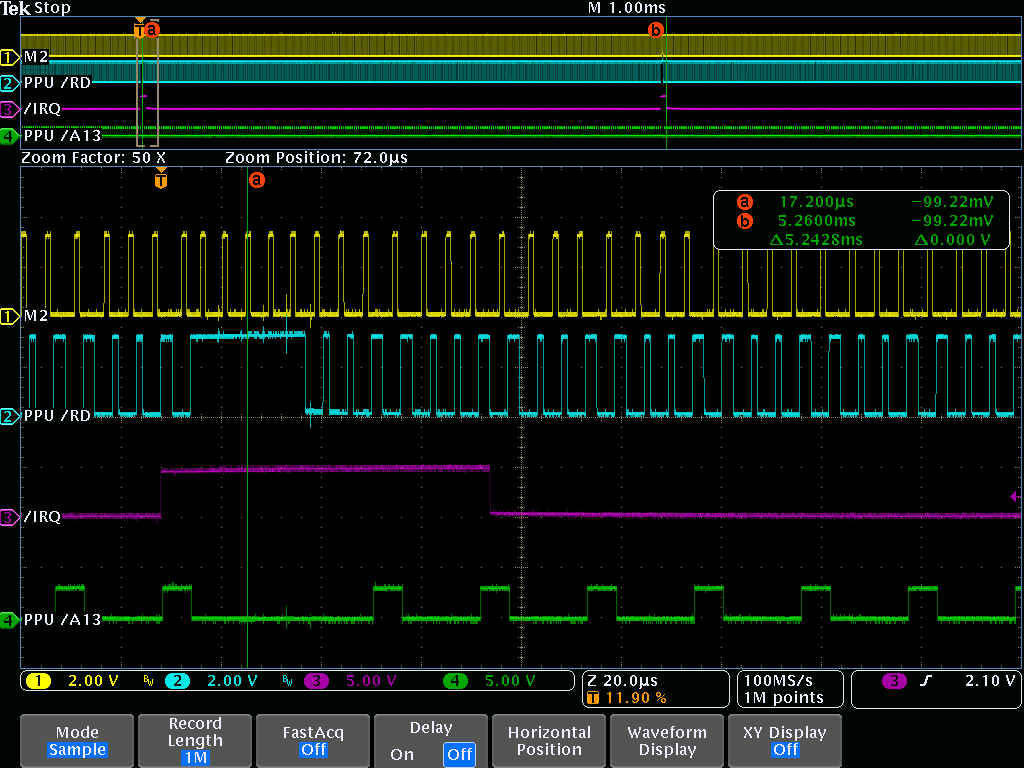

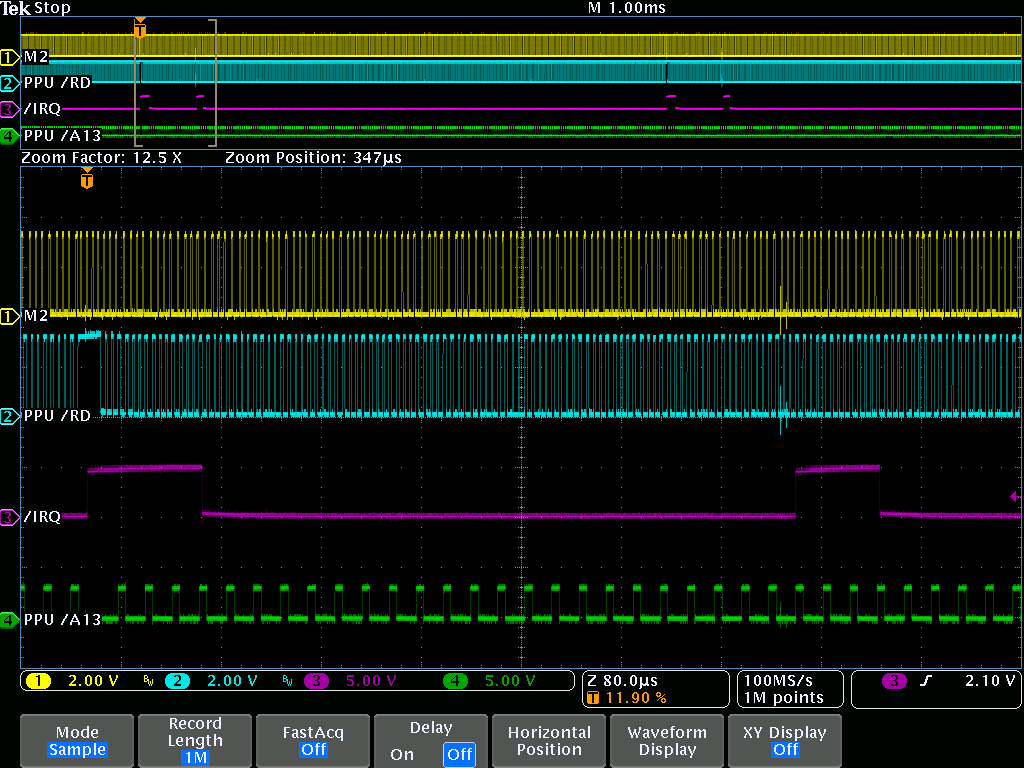

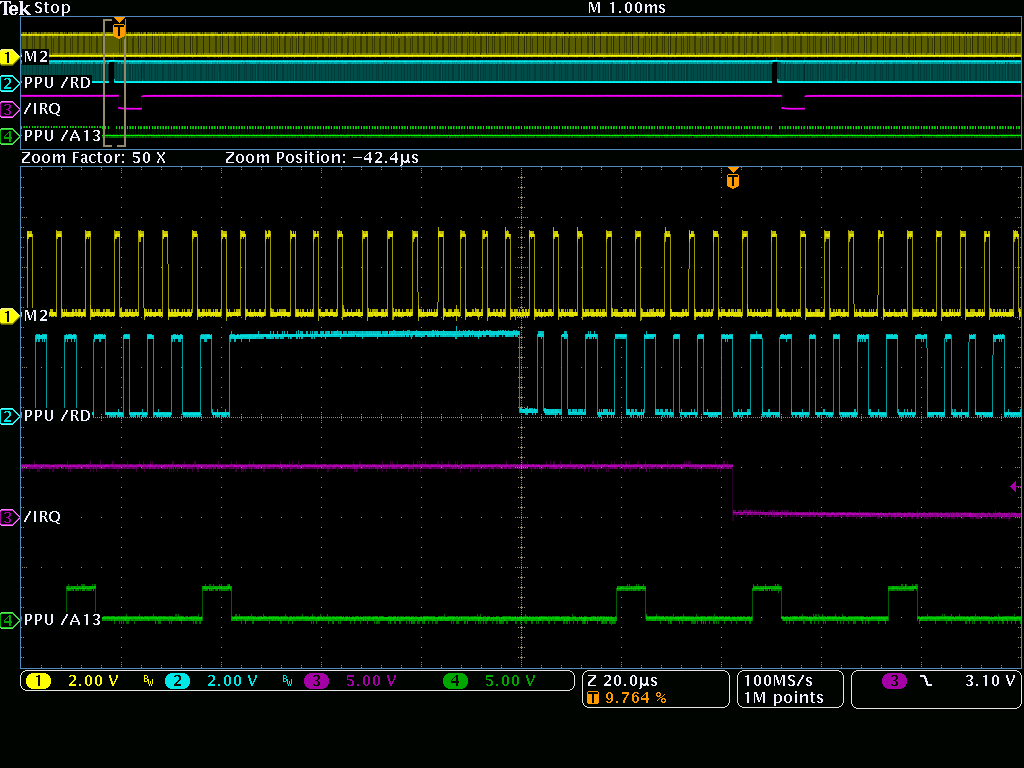

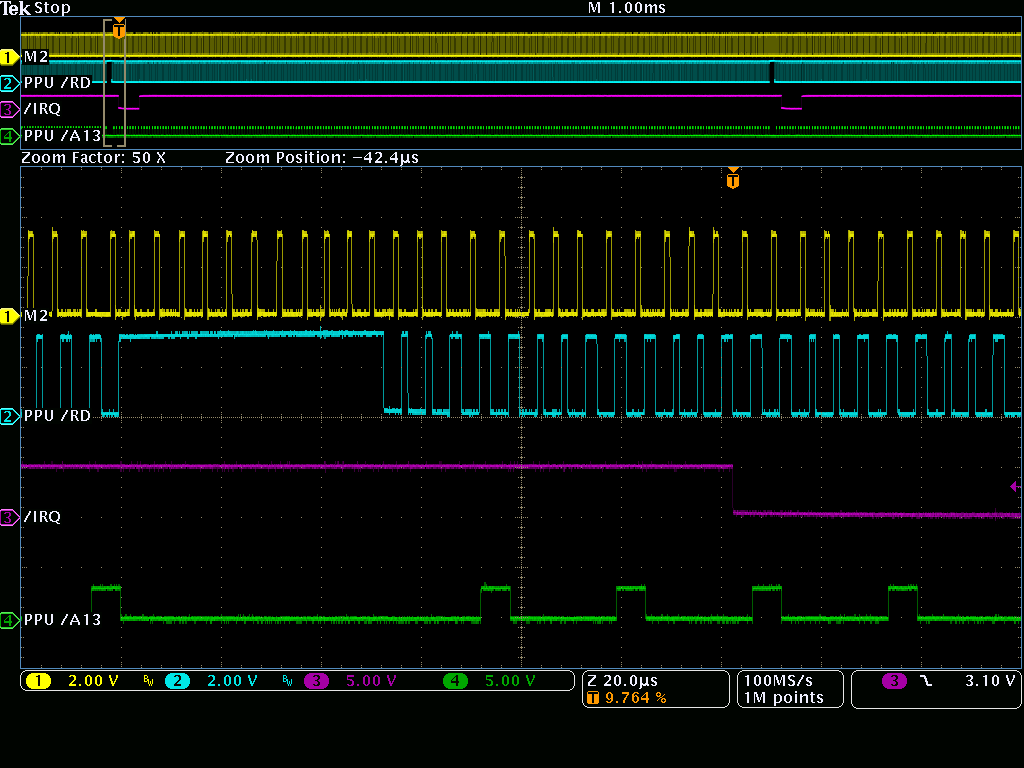

Thanks krzysiobal, I read your thread and now I am able to get the status bit to clear by toggling M2. With my setup, I was able to determine that the MMC5 is very likely to be counting falling edges of M2 for this purpose. I attached a photo explaining how I came to this conclusion, also described below.

I ran the exact same test, once with M2 being high when "in frame" gets asserted, and another time with M2 being low when "in frame" gets asserted, all the while with the CPU address bus pointing to $5204, R/W = 1, /ROMSEL = 1. I then inverted M2 repeatedly until I was able to read "in frame" status bit cleared.

With M2 initially high, I observed that the status must clear either after 2 falling edges or 2 rising edges of M2 (can't tell because you can't read the status with M2 low). With M2 initially low, I observed that it must clear in either 2 falling edges or 3 rising edges. Therefore, common denominator, it must clear in 2 falling edges.

Tomorrow, I will try to recreate the other observations you made, including reading from CPU addresses $FFFA/B and also the other 2 interrupt vectors.

If you have desoldered the MMC5, could you please check if pins 99 & 80 (GND) are internally connected, and same for pins 44 & 4 (VCC)

Also the behaviour of pin 56 (to RAM's VCC) should be examined - why RAM'S VCC is not connected straight to battery. Maybe there is some kind of brown-out detection, when battery's voltage (MMC5 pin 57) drops below certain level, MMC5 drives pin 56 to ground?

krzysiobal wrote:

why RAM'S VCC is not connected straight to battery.

Because all the switchover circuitry is inside the MMC5? They integrated a MM1026 or something similar inside the package.

I used a diode tester on the pins you mentioned. I am using this format:

Pin A -> Pin B

Where A is anode(+) and B is cathode(-) of the test.

VCC pins:

- 44 -> 4: 1.00V

- 4 -> 44: 0.99V

- 4 -> 56: 1.57V

- 56 -> 4: open

- 4 -> 57: 1.98V

- 57 -> 4: open

- 56 -> 57: 2.31V

- 57 -> 56: 1.41V

- 44 -> 57: 2.23V

- 57 -> 44: open

- 44 -> 56: 0.98V

- 56 -> 44: open

GND pins 80 and 99:

Measures 52 ohms or 0.04V diode test, same in both directions.

quickly throwing that in a table:

Code:

vcc4 v44 prgv batt <- to

vcc4 ---- 0.99 1.57 1.98

v44 1.00 ---- 0.98 2.23

prgv hi hi ---- 2.31

batt hi hi 1.41 ----

^from

Have to admit I'm surprised by many of these.

I quickly broke out my NES-ELROM-01 (4-44 shorted by PCB) board and measured a few things:

4+44 → 56 : 0.854V / 1.258V

4+44 → 57 : high / high

56 → 4+44 : high / 1.777V

56 → 57 : high / high

57 → 4+44 : 0.437V / 0.470V

57 → 56 : 0.559V / 0.618V

Two different voltmeters: the left one can't measure diode drops above 1V; the right can't measure diode drops above 2V.

Maybe pins 44/80 are digital vcc/gnd and 4/99 are analog vcc/gnd (used by the amplifier), cause they're all placed together.

krzysiobal wrote:

Maybe pins 44/80 are digital vcc/gnd and 4/99 are analog vcc/gnd (used by the amplifier), cause they're all placed together.

Exactly my theory as well.

I am doing some testing today on setting and clearing the "in frame" status bit. I have not yet tested reading from the vectors on the CPU bus. I have found results that confirm PPU /A13 involvement in setting this status bit. If /A13 = 1 (tested address 0x1FFF), it can set the status, and if /A13 = 0 (tested address 0x3FFF), it can't, except for the initial run with my setup. The status bit

does get set with PPU /RD falling edge when /A13 = 0 for the first run for me, so I am exploring that for an explanation. It would be easy to say "who cares" because it is just the first frame, but it could possibly shed some more clues.

I had suspected that PPU /A13 was latched somehow, as if the MMC5 is using the latched value for PPU /RD falling edge handling. The way my test was written, /A13 would actually start high and I would set M2 low before setting /A13 low. To test if M2 triggered /A13 to latch, I tried setting M2 low

after setting /A13 low. The status bit still got set first time, test fail.

Next, I tried toggling M2 before /RD falling edge. M2 initially high, then low - high - low. Status still got set. M2 high-low-high-low-high-low-high-low. STILL got set. Probably not M2's fault.

Next, I tried putting a 1k pull-down on /A13 so that it was never high from power on, and throughout the test, verified with oscilloscope that it stayed low. The status bit also still got set. This excludes the possibility that /A13 itself triggers its latch. Conclusion thus far: Whatever can latch /A13 apparently has not occurred yet before the first run of the test, and the default latch value is 1.

Next I tried adding a read of $5204, including toggles to M2, before doing the initial PPU /RD falling edge with /A13 low. Status bit still got set. So, the act of reading $5204 is not the trigger for this theoretical latch, and that kind of blows the whole latch theory because I don't do anything else for this test.

As best as I can tell so far, the initial falling edge of PPU/RD ignores /A13. Period.

I am not able to reproduce what I was saying with /A13 now -- I think I goofed something up. What I am seeing now is that the status bit initially gets set when PPU /RD goes low the first time, regardless of /A13. Then once cleared with M2 toggles, I can not get the status bit to set again after that no matter what the value of /A13. Sorry for the confusion on this -- my assumption was that I could set it again, depending on /A13, and wondering why the initial behavior was different. That seems to not be true now.

I need to go back and read your findings better krzysiobal. It looks like you figured all of this out already.

Quote:

I need to go back and read your findings better krzysiobal. It looks like you figured all of this out already.

There must be three PPU read cycles, all of them from the same address and and the address must be any from range $2000-$3fff.

I looked at how reading from CPU address $FFFA and $FFFB can clear the status. I verified it clearing with my setup. I found that the clearing of the bit is asynchronous. At any time that all of the following are true, it immediately clears the status bit:

- M2 = 1 (does not wait for an edge)

- /ROMSEL = 0

- CPU A14 through A3 = 1

- CPU A2 = 0

- CPU A1 = 1

- (CPU A0 = don't care.)

In addition, when I trigger the status bit to set with falling edge of PPU /RD, if I just leave PPU /RD low after that, I am still able to clear the status by reading $FFFA/B with PPU /RD remaining low the whole time.

It does not clear status when reading the other vectors from $FFFC - FFFF.

I don't know what the problem is, but I am not ever able to get the status bit to set again once I have cleared it. I hold the same PPU address and toggle PPU /RD a bunch of times, and the bit never gets set again. I tried with /A13 both high and low. I tried after clearing with $FFFA/B, and tried after clearing with M2 toggles. I only can get it to set 1 time after power up, which coincides with the

first falling edge of PPU /RD, regardless of PPU /A13. I verified with my scope that /A13 is being driven as intended. I am very confused!! Any ideas what I need to do to get the status bit to set a second time?

Well, right after I posted that I had a breakthrough on this.

I was using PPU addresses $1FFF and $3FFF. Both of those are not able to set the status bit. I tried $0000 and $2000, and $2000 IS able to set the bit again. I will continue this to figure out the exact address ranges that are able to set the bit.

I don't know why but just after power up, there need to be the following sequence:

ppu_read from address xxxx

ppu_read from address xxxx

ppu_read from address xxxx

cpu read 5204 <- it will return the in frame bit clear

ppu_read from any address

cpu read 5204 <- it will now set the in frame bit

After that, it status bit gets cleared, 3 ppu reads and then cpu read from $5204 will normally return in frame bit set (and now I checked that xxxx can be any from range $0000-$3fff, probably last time I misschecked something)

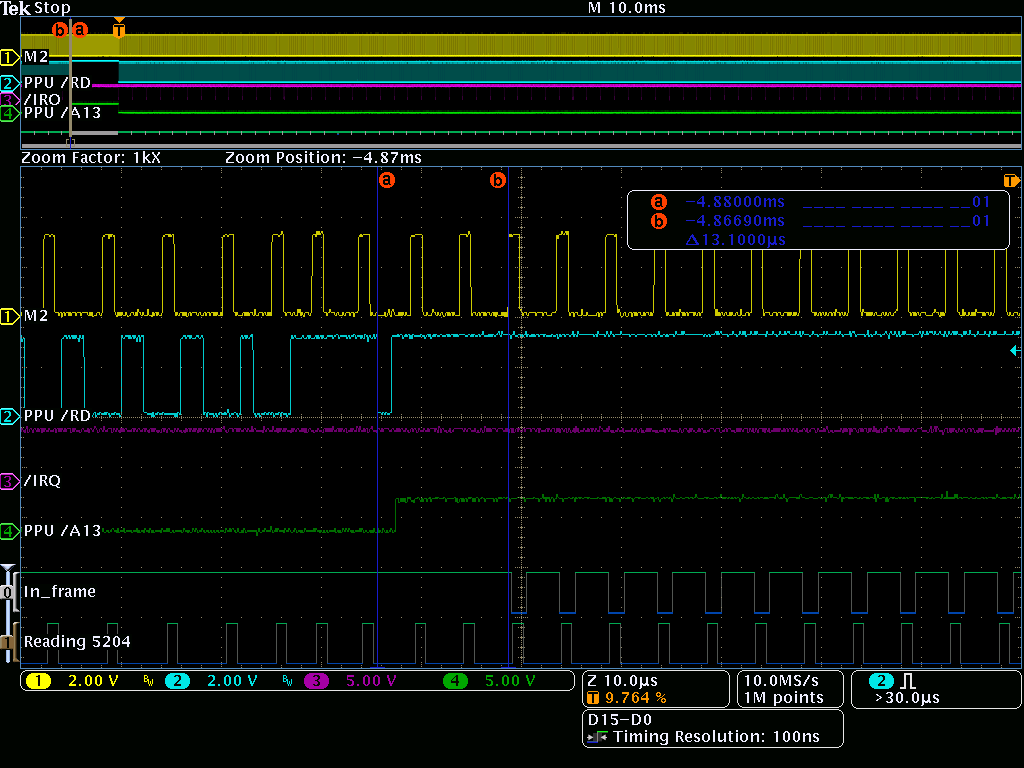

I started a long overnight test on each PPU address, should take many hours. When getting that test running, I found that as I changed things here and there, it took different numbers of PPU /RD toggles to set the status bit and different numbers of M2 toggles to clear the status bit. It didn't seem random - things were very repeatable. For the purpose of this test (i.e. identify all addresses that do and do not cause the status to set), I toggled each of those a bunch of times. There is definitely some counter business going on here. Will be interesting to poke more at it and to see if anything in this test indicates a connection between particular addresses and numbers of toggles.

Results from the test:

"In Frame" status bit is able to be set in the PPU address range $2000 - $3000.

Additional observations:

- As expected, PPU address $0000 did trigger the status bit to be set, based on prior knowledge that the first falling edge of PPU /RD always sets status regardless of PPU address.

- PPU address $3000 IS included. $3001 is the first one not to set the status bit in this test.

- Theory: It could be that after clearing in test $2FFF, the MMC5 has returned to it's "don't care about PPU address, just look for any PPU /RD falling edge" state. (Will test that.)

- PPU Address $2000 set the status on the 4th falling edge of PPU /RD

- All other addresses ($2001 - $3000 (including $3000)) set the status on the first falling edge of PPU /RD

- In this test, clearing of status always occurred on the 3rd falling edge of M2.

Yeah, there is some more complexity behind that, because not always three PPU read cycles set the bit (sometimes, one is just enough and sometimes four).

Now I can confirm that only $2000-$3fff adresses (when comes to three-cycle-read) are able to set the bit.

You were able to get the status bit to set with PPU address range $3001 - $3FFF? I tested each and every PPU address and gave 10 falling edges on PPU /RD, and nothing in that address range set the status bit for me.

My chip is marked MMC5A, is that what yours is marked?

Did a quick test, running PPU address range limited to just $2FF0 through $3003. Was able to repeat the status being set from beginning up to $3000 and then not set on $3001/2/3. I then made the test skip address $3000, so it tested $2FFE, $2FFF, [skipped], $3001. And the status did get set on $3001 this way and not on $3002. So it looks like it always is accepting the next one regardless of PPU address in this situation.

I am trying to keep in mind that this strange counter-type handling might be related to the difference between one scanline to the next vs. starting a whole new frame after v-blank. I might need to learn more about the PPU and how it accesses memory for different purposes.

That does smell like there's something off with your test. Try testing addresses randomly?

I have MMC5A from Just Breed.

Actually, the scanline counter is quite simple - at start of each PPU read cycle it just looks for the last three 3 PPU read addresses and whenever it sees three from same address, it increments its value.

What is also interesting is that even if the $5204.7 is set, /IRQ is asserted only if M2 toggles (if M2 stops toggling, it it deasserted) - same goes for the /IRQ asserted from $5209.

I just ran the same test except with random PPU address instead of sequential PPU address. I tested 10,000 random PPU addresses. The address range does correlate - the status bit could only get set in address range $2000 through $2FFF for me.

I noticed that in all cases after clearing the status, the next falling edge of PPU /RD always set the status again regardless of address, on the first falling edge. Will review the data more closely this evening.

Here is my data. I put some conditional formatting colors to make it easier to see. Some clear patterns emerge in this test.

I have found that the M2 counter for clearing status, resets its count any time PPU /RD has a falling edge, regardless of PPU address staying the same or changing. I found this by inserting PPU /RD toggles between each M2 toggle. It could never clear the status in this test.

Yes, that's how it works - there must be three or more CPU cycles without PPU read between to clear the in-frame bit.

Okay, my findings agree with that. You said 3 or more cycles -- not sure how literally you mean that. Have you seen it take more than 3 M2 falling edges to clear the status? I have only ever seen it take exactly 3 that I am aware of.

I still see a very persistent range of PPU addresses that can set the status which is different that yours:

$0000

-> Doesn't set

$1FFF

$2000

-> Does set after counting PPU /RD falling edges

$2FFF

$3000

-> Doesn't set for me, does set for you.

$3FFF

How can yours set in range $3000 - 3FFF but not mine? Do you write to any registers or drive any other inputs low at the beginning of your test?

Quote:

Okay, my findings agree with that. You said 3 or more cycles -- not sure how literally you mean that. Have you seen it take more than 3 M2 falling edges to clear the status? I have only ever seen it take exactly 3 that I am aware of.

I mean 3.

Quote:

How can yours set in range $3000 - 3FFF but not mine? Do you write to any registers or drive any other inputs low at the beginning of your test?

No, you are right, only $2000-$2fff can set it. I haven't checked that before with so many datails.

Okay. I am trying to think of this from the perspective of FPGA or CPLD, that is why I am so paranoid about edges and what latches and what happens asynchronously, etc.

Do you agree that the in-frame status bit works like this?:

Code:

// Declaration / initial values:

UInt16 prev_ppu_address = ? / don't care

bool always_set_in_frame_status_next_ppu_read = true; // Default true: first falling edge of PPU /RD always sets in_frame_status regardless of PPU address and set counter.

int set_counter = 0; // counts PPU /RD falling edges

int clear_counter = 0; // counts M2 falling edges

void on_ppu_rd_falling_edge( void )

{

clear_counter = 0; // Observation: Always resets M2 counter regardless if PPU address stayed the same or changed.

if(prev_ppu_addr != ppu_addr)

{

set_counter = 0;

prev_ppu_addr = ppu_addr;

}

if( true == always_set_in_frame_status_next_ppu_read )

{

in_frame_status = 1;

always_set_in_frame_status_next_ppu_read = false;

}

else if( ppu address is in range $2000 to 2FFF ) // Observed this range.

{

set_counter++;

if(set_counter >= 4)

{

in_frame_status = 1;

}

}

}

void on_m2_falling_edge (void)

{

if(in_frame_status = 1)

{

if(PPU /RD is high) // Observation: with PPU /RD held low, status can not clear with M2 toggles.

{

clear_counter++;

if(clear_counter >= 3) // Observation: always clears on the 3rd falling edge of M2, considering /RD had not reset the counter.

{

always_set_in_frame_status_next_ppu_read = true;

in_frame_status = 0

}

}

}

}

void combinational_logic (void)

{

'and' these:

M2, !(/ROMSEL), CPU A14,13,12,11,10,9,8,7,6,5,4,3,!2,1,in_frame_status

result 1 -> always_set_in_frame_status_next_ppu_read = true, in_frame_status = 0

// Observation: this part does not care about PPU /RD even if it is held low.

}

I am wondering if there is some way to simplify this - maybe the counters can be combined into 1 counter and the status bit is one of the bits of the counter, etc. I will think about it some more.

Edit:

Oops, nothing ever clears always_set_in_frame_status_next_ppu_read. hmmm...

Edit 2: fixed I think

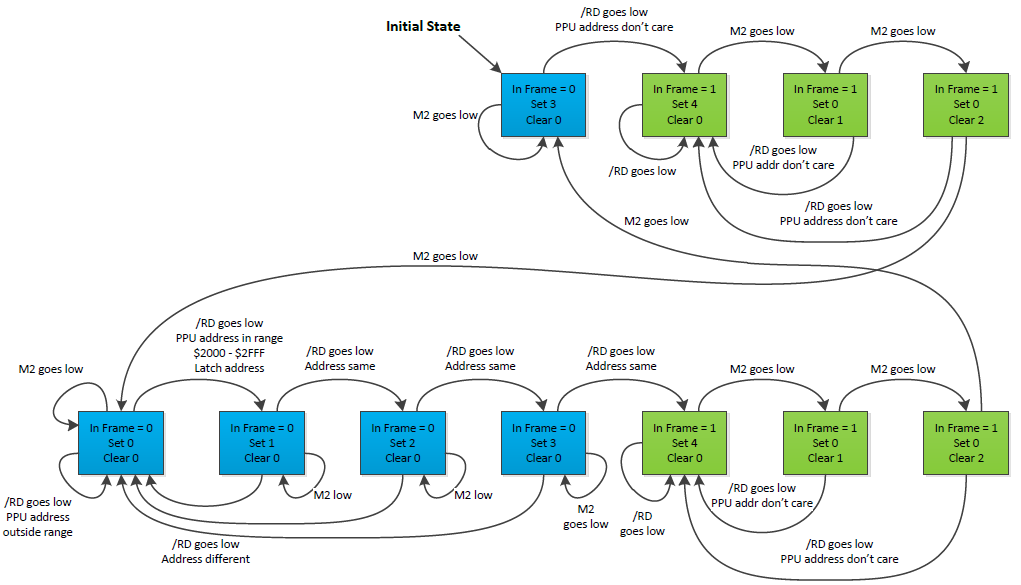

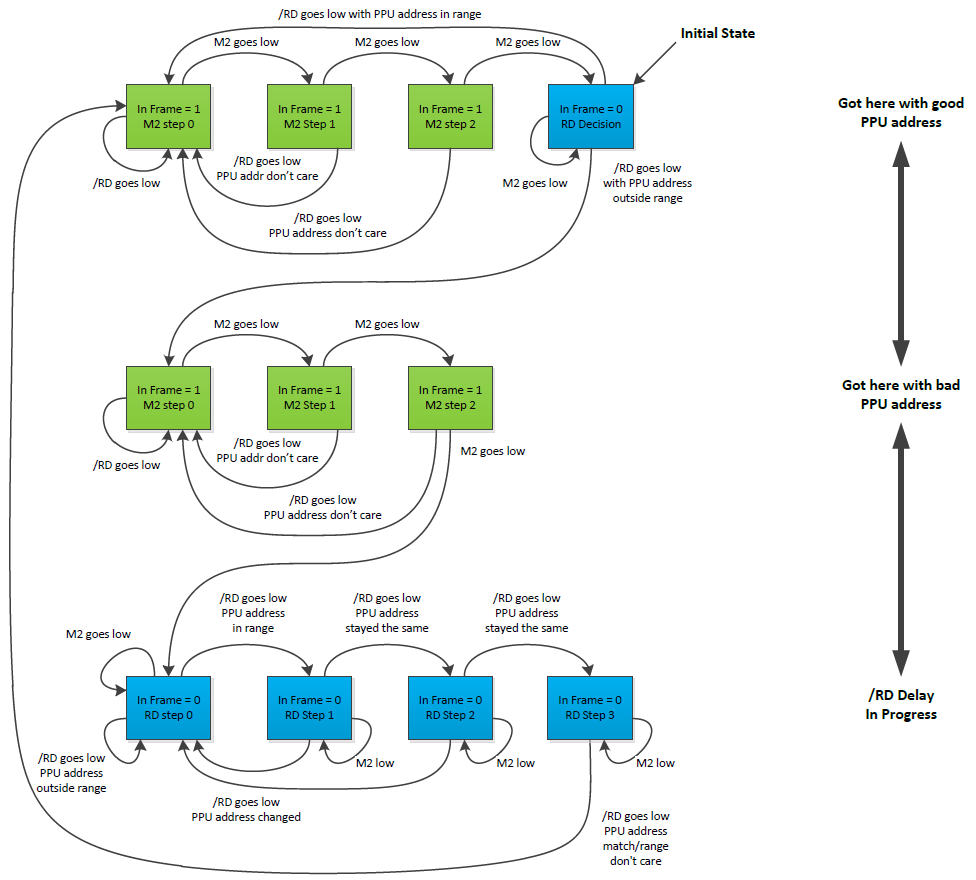

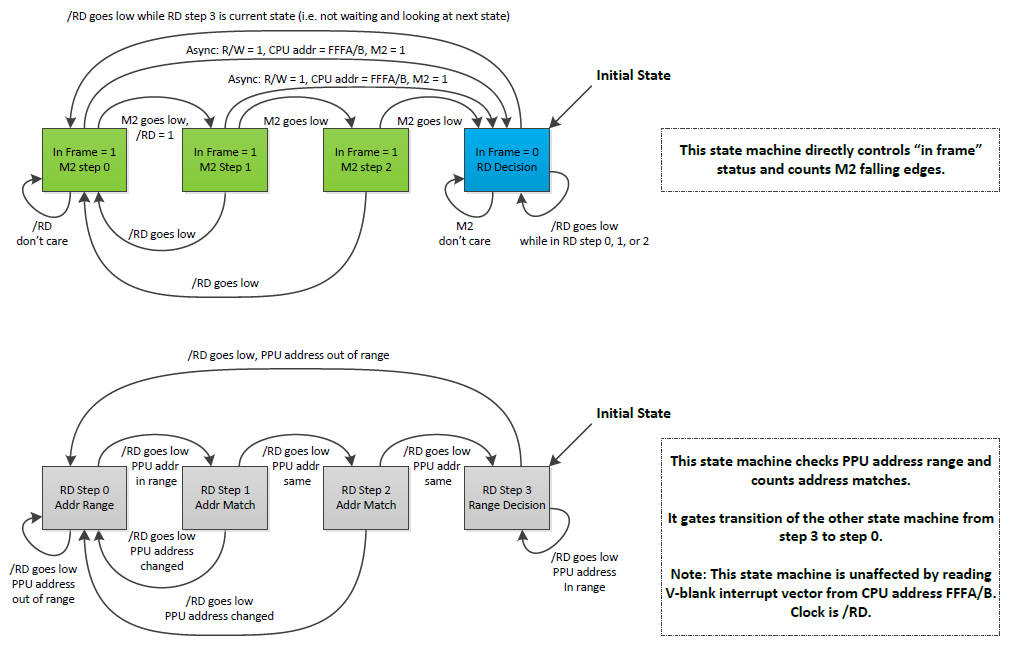

I made a state diagram of how we think it works. I think this is a better approach than pseudo-code. I would like to try to verify each arrow in the diagram. If everything checks out, then I think we can feel pretty confident that we nailed down M2 and /RD interaction with the in frame status bit. Reading from CPU address $FFFA/B is not shown in this diagram.

Attachment:

in_frame_bit_states.PNG [ 66.14 KiB | Viewed 4462 times ]

in_frame_bit_states.PNG [ 66.14 KiB | Viewed 4462 times ]

Edit: Something isn't right here because I know that you can loop through just the top 4 boxes if you keep reading PPU addresses in range 2000-2fff. This diagram shows the 4x /RD every other read even when PPU addresses remain in this range. Will think about how to fix the diagram.

Edit 2: This is better:

Attachment:

in_frame_bit_states_2.PNG [ 80.42 KiB | Viewed 4449 times ]

in_frame_bit_states_2.PNG [ 80.42 KiB | Viewed 4449 times ]

Edit 3: This still isn't right because it alternates between caring and not caring about the PPU address when the address is always in range... I will get this, probably a few more revisions...

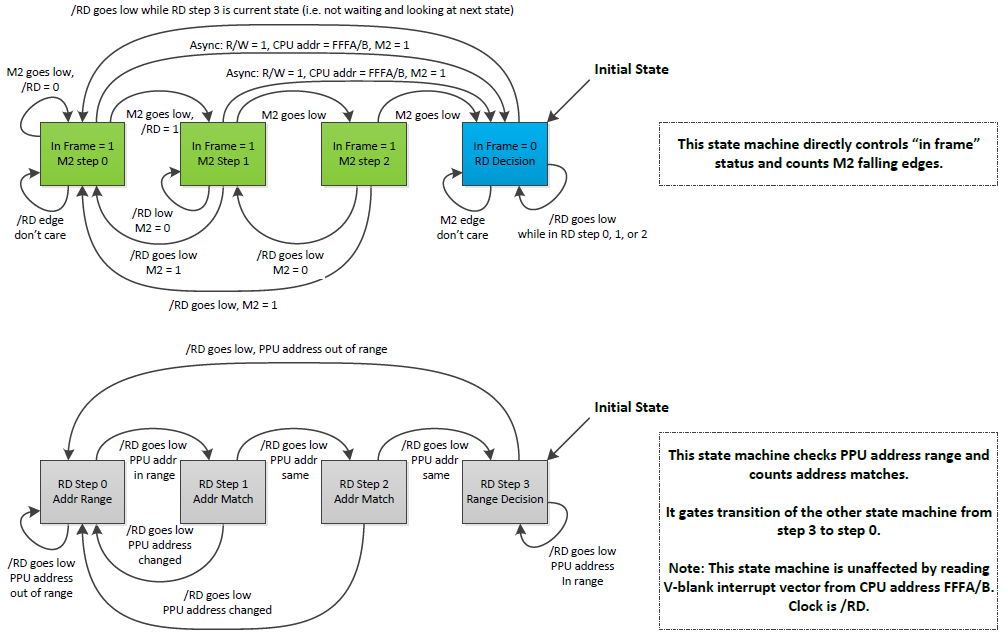

Edit 4: More improvements:

Attachment:

in_frame_bit_states_3.PNG [ 82.18 KiB | Viewed 4443 times ]

in_frame_bit_states_3.PNG [ 82.18 KiB | Viewed 4443 times ]

Edit 5: I have looked at the diagram in edit 4 a fair bit now and I am feeling pretty good about it now. I think I will print it and start testing each arrow and checking them off.

New discovery:

It turns out that "RD Step 3" does not require a matching PPU address, or even a PPU address in range. In fact I set PPU address to 0x0000 and it still did the big loop around to the top. This finding removes 1 of the arrows from the diagram.

Attachment:

in_frame_bit_states_4.PNG [ 80.85 KiB | Viewed 5619 times ]

in_frame_bit_states_4.PNG [ 80.85 KiB | Viewed 5619 times ]

Edit:

I have checked all arrows now and I believe that this diagram is correct. Additional things not shown or tested in this diagram:

- Any potential interaction with PPU /WR (none known)

- Reading from each of the 2 V-blank interrupt vector bytes from each of the 6 green boxes

- Any interaction with SL3 (pin 98), I am completely clueless on this one.

Edit 2:

I added the v-blank FFFA/B reads to the diagram. To make the arrows lay out better, I moved RD step 0.

Testing FFFA/B in each state divulged an interesting new connection from the 3rd /RD delay state back to the initial state. Normally, from state "RD step 3", falling edge of /RD always leads a 'good' sequence of green boxes (regardless of PPU address range), after which, another good or bad sequence of green boxes must also occur. However, if you sneak in a read from FFFA/B in "RD step 3", then it then it DOES matter if the PPU address is in range. It can go directly to the bad sequence of green boxes. This observation corresponds to a state change to the initial state.

The diagram did get a little more busy with the FFFA/B stuff added, but no previous findings were changed.

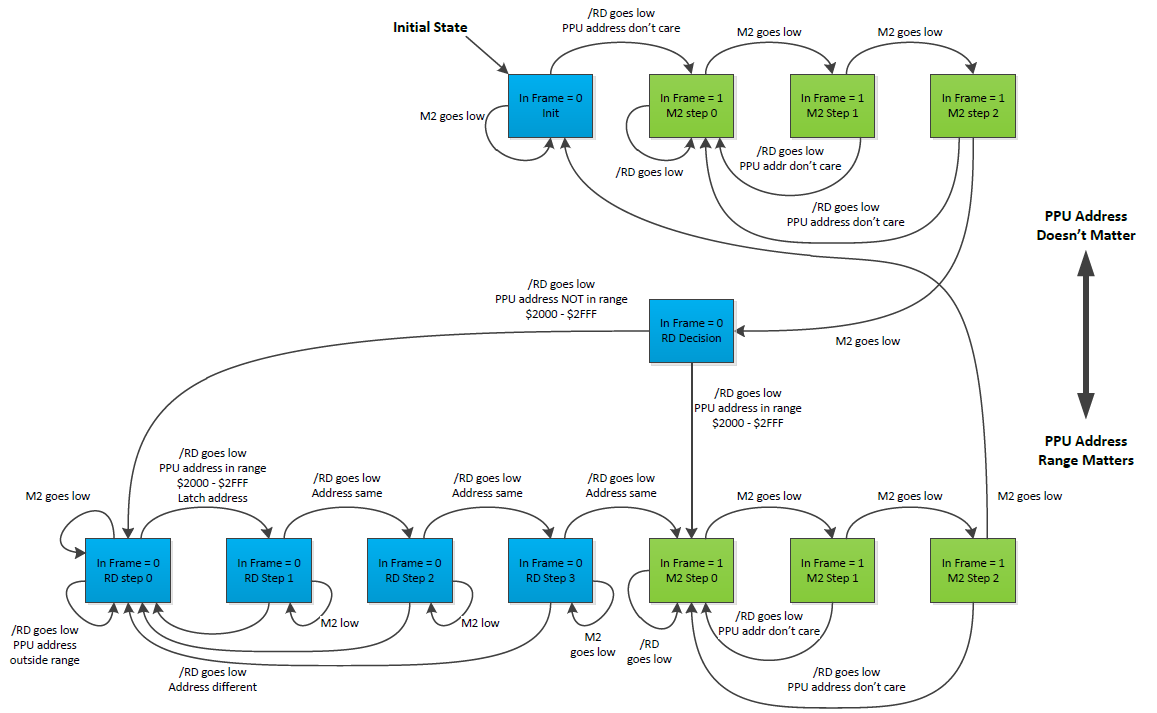

Attachment:

in_frame_bit_states_5.PNG [ 100.88 KiB | Viewed 5611 times ]

in_frame_bit_states_5.PNG [ 100.88 KiB | Viewed 5611 times ]

Edit 3:

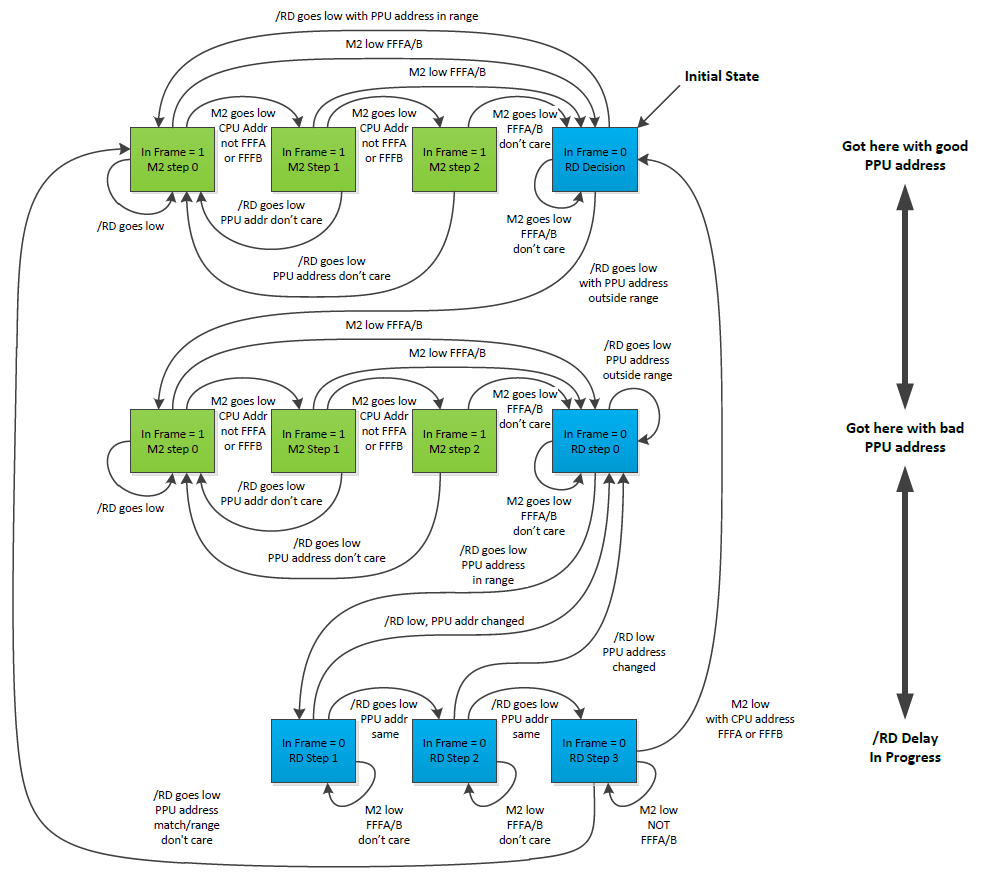

There is still more going on here with reading $FFFA/B. Say that I am in a "step 0" green box. The PPU address is in range and I don't touch it. Then I read CPU bus FFFA. I switch the CPU bus back to reading the status register and the status bit went to 0, as expected. Then on the 3rd falling edge of PPU /RD, the status gets set again. Coincidentally, this is the same spot it would have been set again going through the normal process of /RD delay had none of this ever happened, which leads me to believe the /RD delay states operate independently of what is going on elsewhere in this diagram. I tested this by reading FFFA within a "step 1" box. Now it was the 2nd falling edge to set the status again, which again coincides where it would have been set with normal /RD delay. I think this proves that the state of the RD delay must be operating independently from the other stuff that is going on.

I am thinking that this is going to blow up a little more complicated until we start to notice more patterns, then we can simplify it back down into its more general state of existence. I really truly believe that this is just a counter or two and some gates.

It is still pretty early on this new theory but it is making a lot of sense. I finally got rid of the duplicated 3 green / 1 blue box rows.

Attachment:

in_frame_bit_states_6.PNG [ 76.83 KiB | Viewed 5594 times ]

in_frame_bit_states_6.PNG [ 76.83 KiB | Viewed 5594 times ]

Edit 1:

Issue found: The big top arrow on the gray boxes causes the /RD delay to always occur after any time the status bit is cleared. We have clearly observed the delay is skipped if the next PPU address is in range. So something is wrong with that arrow.

Edit 2:

Additional tweaks made:

Attachment:

in_frame_bit_states_7.PNG [ 78.37 KiB | Viewed 5584 times ]

in_frame_bit_states_7.PNG [ 78.37 KiB | Viewed 5584 times ]

Edit 3:

I am still feeling pretty good about this one, except 1 observation I had before that is not captured. With PPU /RD held low, I observed that the status bit could not be cleared with M2 toggles. But with PPU /RD held low, it could be cleared with reading 0xFFFA/B.

Edit 4:

More tweaks per edit 3:

Attachment:

in_frame_bit_states_8.PNG [ 73.19 KiB | Viewed 5572 times ]

in_frame_bit_states_8.PNG [ 73.19 KiB | Viewed 5572 times ]

Thanks for updating the arrows in my new MMC5 ASCII pinout in the wiki Lidnariq, I didn't realize how incomplete I left that!

Here are some tests that I did today to test the state diagram, especially focusing on reading from vblank interrupt vector address $FFFA. I am thinking that the diagram is just about exactly right now -- I am not able to find any example that disagrees with the diagram anymore. I have not tried anything with PPU /WR; maybe I should try toggling that pin from each state. I am open to any ideas for additional tests.

I am thinking it is quite likely that the clock of the top state machine is /RD 'and' M2. This would explain why /RD held low prevents M2 toggles from clearing status. If this is true, M2 step 1 should also not transition back to step 0 if M2 remains low after entering step 1, then /RD goes low and back high, and then finally M2 goes high. If true, 2 additional M2 falling edges with /RD high should clear the status in this case. I will test that tonight.

Test 1: RD state machine unaffected by reading FFFA/B, while in M2 step 0.

1. Set M2 = 1, R/W = 1, /RD = 1.

2. Get into this state:

*000

000*

- Set PPU address = $2000

- Set PPU /RD low and then high, 5 times

3. Set CPU address = $FFFA, then back to status register.

- Observation - status bit cleared.

Hypothetically, we are in this state:

000*

000*

4. Set /RD low (PPU address still $2000 and /RD still high since step 2.)

- Observation - status bit did set again right away.

*000

000*

Test 2: RD state machine unaffected by reading FFFA/B, while in M2 step 1.

1. Set M2 = 1, R/W = 1, /RD = 1.

2. Get into this state:

0*00

000*

- Set PPU address = $2000

- Set PPU /RD low and then high, 5 times

- Set M2 low and then high, once.

3. Set CPU address = $FFFA, then back to status register.

- Observation - status bit cleared.

Hypothetically, we are in this state:

000*

000*

4. Set /RD low (PPU address still $2000 and /RD still high since step 2.)

- Observation - status bit did set again right away.

*000

000*

Test 3: RD state machine unaffected by reading FFFA/B, while in M2 step 2.

1. Set M2 = 1, R/W = 1, /RD = 1.

2. Get into this state:

00*0

000*

- Set PPU address = $2000

- Set PPU /RD low and then high, 5 times

- Set M2 low and then high, twice.

3. Set CPU address = $FFFA, then back to status register.

- Observation - status bit cleared.

Hypothetically, we are in this state:

000*

000*

4. Set /RD low (PPU address still $2000 and /RD still high since step 2.)

- Observation - status bit did set again right away.

*000

000*

Test 4: RD state machine unaffected by reading FFFA/B, while in M2 step 3.

1. Set M2 = 1, R/W = 1, /RD = 1.

2. Get into this state:

000*

000*

- Set PPU address = $2000

- Set PPU /RD low and then high, 5 times

- Set M2 low and then high, 3 times.

- Observation - status bit on 3rd M2 falling edge.

3. Set CPU address = $FFFA, then back to status register.

- Observation - status bit stayed clear.

Hypothetically, we have remained in this state:

000*

000*

4. Set /RD low and then high (PPU address still $2000 and /RD still high since step 2.)

- Observation - status bit did set again right away.

*000

000*

Test 5: RD falling edge affecting step 3 in both state machines at the same time.

1. Set M2 = 1, R/W = 1, /RD = 1.

2. Get into this state:

*000

000*

- Set PPU address = $2000

- Set PPU /RD low and then high, 5 times

3. Set CPU address = $FFFA, then back to status register.

- Observation - status bit cleared.

Hypothetically, we have are in this state:

000*

000*

4. Set PPU address = $1FFF (different and out of range)

5. Set /RD low and then high (/RD had still been high since step 2.)

- In theory, the M2 state machine uses the "current state" of the RD state machine.

- Observation - status bit did set again.

Theory not disproved. Hypothetically, the current state is now:

*000

*000

6. Return to this state:

000*

*000

- Set CPU address = $FFFA, then back to status register.

- Observation - status bit cleared.

7. Set /RD low and then high (/RD had still been high since step 5, PPU address still $1FFF since step 4.)

- status remains cleared.

000*

*000

8. Set PPU address in range ($2000)

9. Set /RD low and then high 5 times

000*

0*00

000*

00*0

000*

000*

*000

000*

- Observation - Status became set on the 4th falling edge of /RD.

Okay, I am pretty sure I found something that does not match the "top state machine clocked by M2 'and' /RD" theory.

Test 1:

The test wrote:

PPU address = $2000 for entire test.

1. Get into this state, /RD and M2 high:

*000

000*

2. Set M2 low and keep it low. State should now be:

0*00

000*

3. Toggle /RD lots of times, ending up high. If the clock of the top state machine is /RD 'or' M2, states should be unaffected:

0*00

000*

4. Set M2 back high. States still unaffected

0*00

000*

5. Set M2 low and back high.

00*0

000*

6. Set M2 low and back high a 2nd time

000*

000*

Sure enough, this test passed, status went low after 2nd M2 toggle at the end.

HOWEVER: if I modify the test so that test step 2 starts in M2 step 2:

The test wrote:

PPU address = $2000 for entire test.

1. Get into this state, /RD and M2 high:

*000

000*

1b. Set skip to next state in top state machine by setting M2 low and back high once.

0*00

000*

2. Set M2 low and keep it low. State should now be:

00*0 (?)

000*

3. Toggle /RD lots of times, ending up high. If the clock of the top state machine is /RD 'or' M2, states should be unaffected:

00*0 (?)

000*

4. Set M2 back high. States still unaffected

00*0 (?)

000*

5. Set M2 low and back high.

000* <- status NOT cleared here, so it is not in this state.

000*

6. Set M2 low and back high a 2nd time

000* <- status did clear this time

000*

In this unrealistic situation, it takes 1 more M2 falling edge to clear the status bit than predicted. Though this condition can't probably happen in a real Famicom, it is still important because it shows us that our understanding is not yet complete.

Edit:

I don't feel good about it but here it is:

Attachment:

in_frame_bit_states_9.PNG [ 77.34 KiB | Viewed 5512 times ]

in_frame_bit_states_9.PNG [ 77.34 KiB | Viewed 5512 times ]

It just doesn't feel right, the previous one felt better. I think I need to think about how to interpret those results and take a fresh look at the test tomorrow and make sure I didn't goof it up somehow.

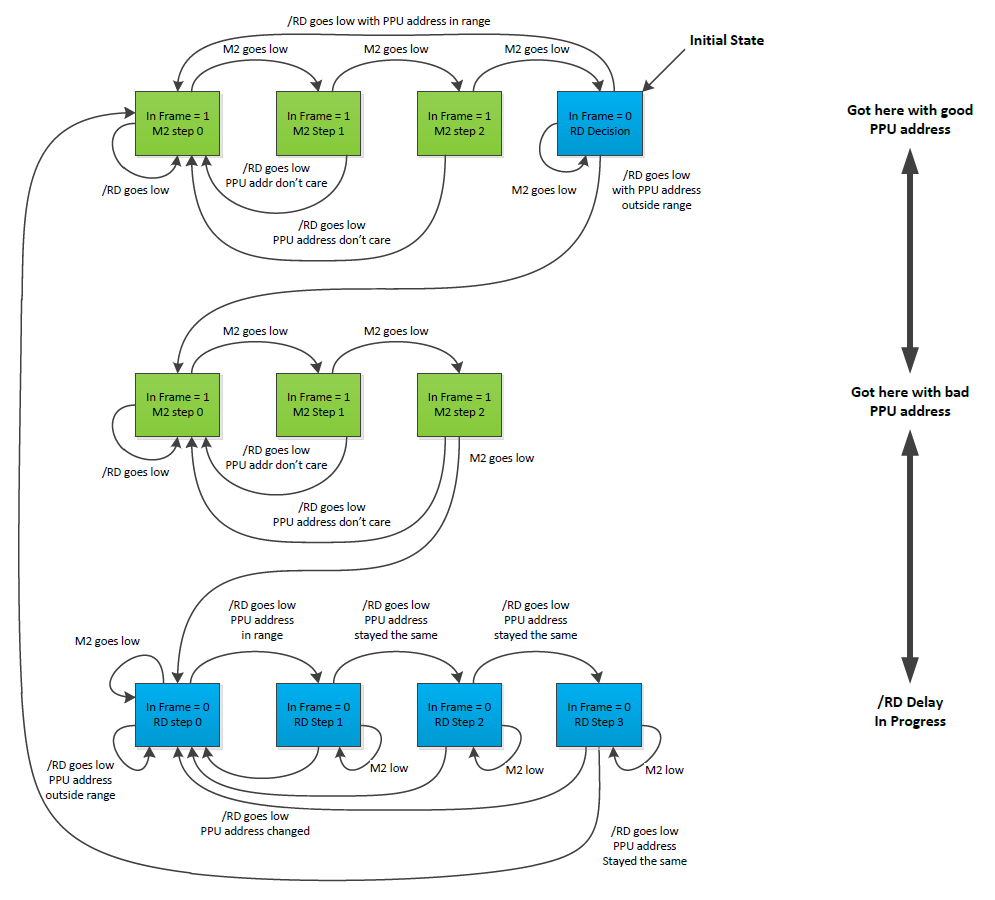

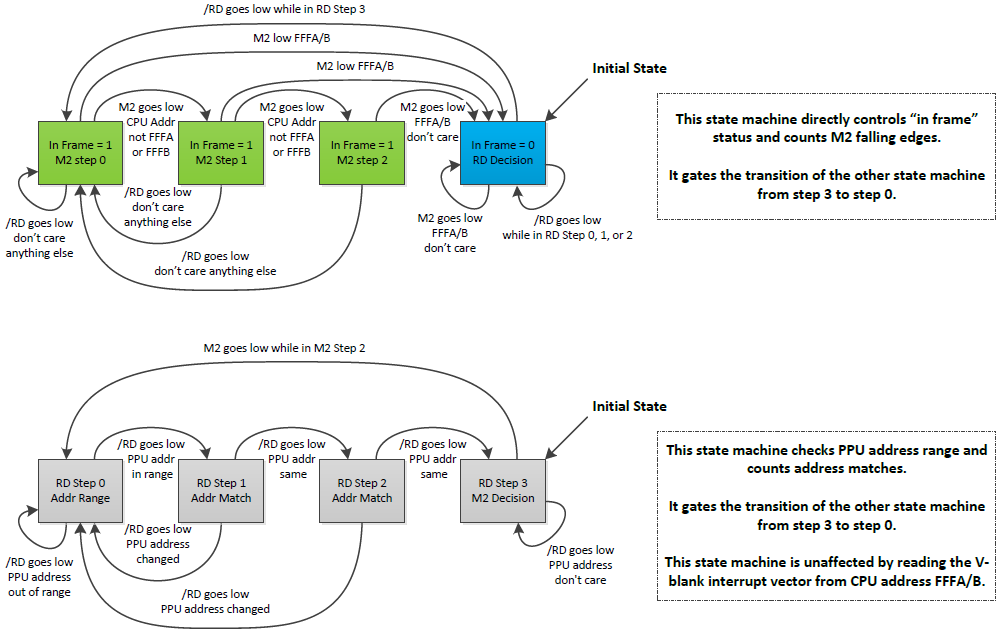

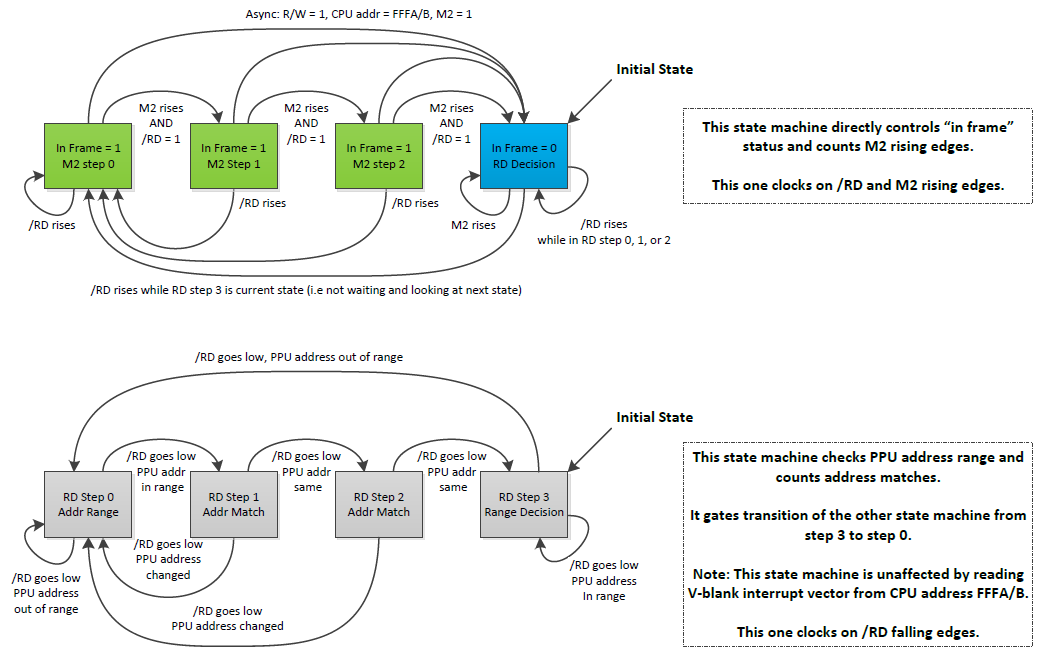

More testing is still necessary, but I have come up with a diagram that explains everything that I have observed so far, including 4 additional tests described below. This approach modified the top state machine to trigger on rising edge, and it left the bottom state machine triggering on falling edge. I did not yet test or think about the bottom state machine's edge in light of the changes to the top state machine. The triggering edge of M2 is tricky because you can't read the status with M2 low.

Attachment:

in_frame_bit_states_A.PNG [ 77.17 KiB | Viewed 5475 times ]

in_frame_bit_states_A.PNG [ 77.17 KiB | Viewed 5475 times ]

It now passes all of these tests (below). Test 1, 2, 3, and 4 failed with previous diagrams.

All tests start in this state by setting PPU address = $2000 and toggling PPU /RD lots of times:

*000

000*

Test begins in this state with M2 = 1, /RD = 1, status bit set.

Control Test (already passed) wrote:

- M2 falls

- M2 rises

- M2 falls

- M2 rises

- M2 falls

- M2 rises <- status bit got cleared here.

Test 1 wrote:

- M2 falls

- RD fall and rise lots of times, ending high

- M2 rises

- M2 falls

- M2 rises

- M2 falls

- M2 rises <- status bit got cleared here.

Test 2 wrote:

- M2 falls

- M2 rises

- M2 falls

- RD fall and rise lots of times, ending high

- M2 rises

- M2 falls

- M2 rises

- M2 falls

- M2 rises <- status bit got cleared here.

Test 3 wrote:

- M2 falls

- RD falls

- M2 rises

- RD rises

- M2 falls

- M2 rises

- M2 falls

- M2 rises

- M2 falls

- M2 rises <- status bit got cleared here.

Test 4 wrote:

- M2 falls

- M2 rises

- M2 falls

- RD falls

- M2 rises

- RD rises

- M2 falls

- M2 rises

- M2 falls

- M2 rises

- M2 falls

- M2 rises <- status bit got cleared here.

New problem. It seems like I have just fixed some complicated status clearing sequences, but one of the first things I knew about this was that PPU /RD falling edge sets the status, and that seems to have broken in this latest diagram. I need to verify that is true, and if so, make more changes to the diagram. I have been toying with the idea that the top state machine only clears and the bottom state machine only sets. I think I will think about that idea some more.

I am really impressed in the way you analyze this, but I personally thing that this complexity might be some kind of implementations's side effect how status setting was meant to work.

if I were you, I wouldn't spend on it so much time, there are many other interesting aspects of MMC5 to analyze and replicationg exactly that status bit behaviour will be hard too.

Thanks krzysiobal. I feel like I am still getting closer on this status bit -- as it is, I think this diagram is very good at explaining the behavior, but there are still some corner conditions that don't quite match up yet. I think that there is more I can do with this bit before feeling good about it and moving on to something else. These issues could potentially make graphical glitches if implemented this way. I want my trippy backgrounds to be perfect.

I mentioned my idea where the top state machine clears status and the bottom one sets status, but the interaction of PPU /RD falling edge causing a state change in both state machines at the same time is really integrated into my observations so far. That feature really explains a lot of what we see here, so it is hard to consider giving that up. A new idea I had over lunch today was that maybe all of the PPU /RD logic in the top state machine operates asynchronously, similar to reading $FFFA/B. I think I can test that theory like this:

- Get into this state, just like recent tests:

*000

000*

status = 1, /RD = 1, M2 = 1 - Never touch M2 in this test.

- Set PPU /RD low, leave it low.

- Read $FFFA. It should put us into this state:

000*

000* - Read status. If /RD logic is asynchronous like $FFFA, status should automatically set and we should be in this state:

*000

000* - If status is still not set, rise /RD, check status again. If it got set, it waited for rising edge PPU /RD.

- If status is still not set, fall /RD, check status again. If it got set (It definitely should be set by now), it waited for falling edge PPU /RD.

Will try it later tonight.

Edit:

It definitely waited until the last step to set the status bit. It apparently does wait for a PPU /RD falling edge, not asynchronous.

In other news, I recently hooked up an LED bargraph display to all 8 unknown pins. I keep an eye on it for any blinks/flashes during these tests now. All 8 have always been output high or open bus (can't tell the difference with this setup) so far.

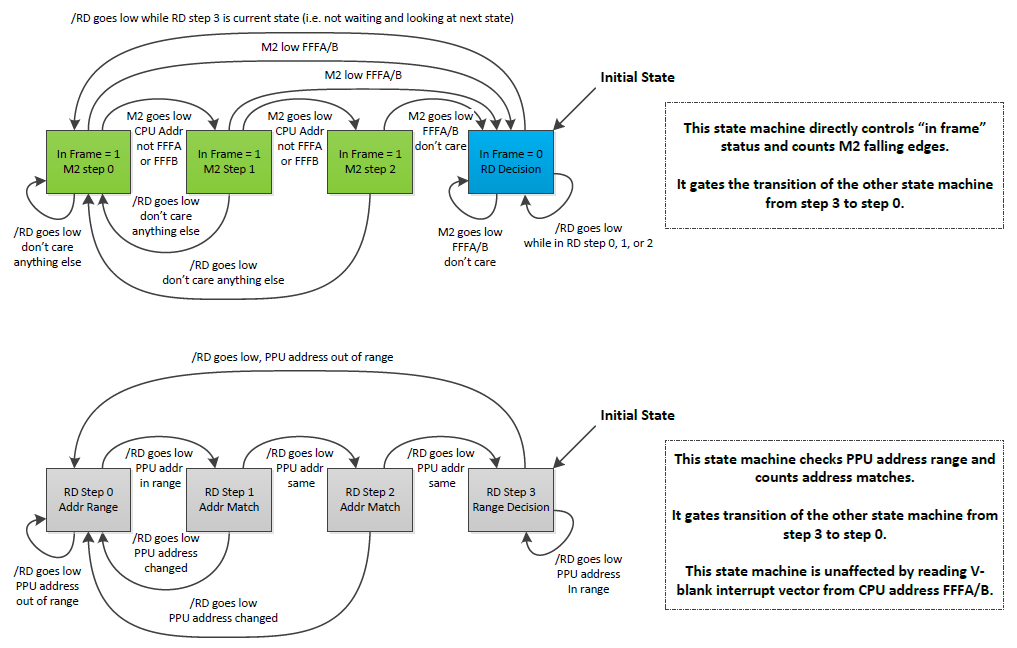

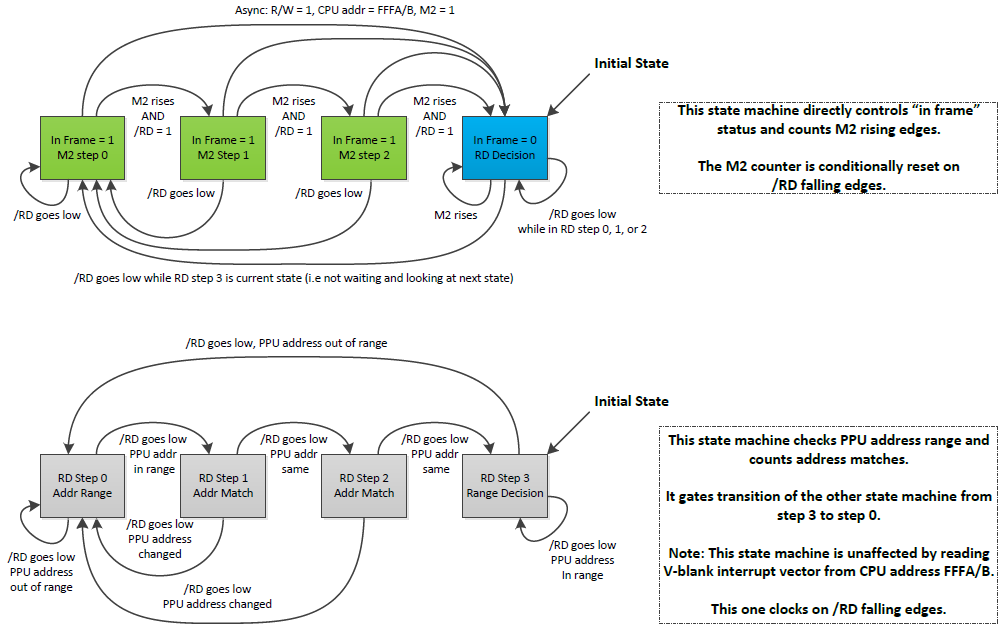

Edit 2:

I looked into the /RD edge trigger of the top state machine. We know for a fact that exiting the blue box and going back to M2 step 0 happens on the falling edge of /RD. However, due to the 'and' logic with /RD when stepping from M2 step 0, 1, 2, it might not be possible to tell for certain which edge of /RD takes you from M2 step 1 to step 0, or M2 step 2 to step 0. It actually might not

matter. We do know that /RD is falling edge when exiting the blue box, so in keeping with this, I made all /RD falling edge and all M2 rising edge. I feel pretty satisfied with this diagram now -- I think that it accurately describes the status bit. I think we are good enough with this bit now to proceed to other MMC5 things, definitely in agreement with you krzysiobal. Here is the final 'in frame' status bit diagram, for now anyway.

Attachment:

in_frame_bit_states_B.PNG [ 75.45 KiB | Viewed 5407 times ]

in_frame_bit_states_B.PNG [ 75.45 KiB | Viewed 5407 times ]

I think I could put this diagram in the wiki. What should I look at next?

On the topic of the IRQ-related register at $5209, is there any possibility that it's actually a cycle counter initialized by writing to $5207-$5208? Having a register that just triggers an IRQ when you write to it seems slightly useless, at least in my opinion.

I agree, that does seem sort of useless without some cycle counting or something, very similar to the DAC interrupt. Why would you need an interrupt if you already know it is going to happen immediately? It seems like there may be more to these things. I will try poking at it some time soon.

I am interested to see this done.

Quietust wrote:

On the topic of the IRQ-related register at $5209, is there any possibility that it's actually a cycle counter initialized by writing to $5207-$5208? Having a register that just triggers an IRQ when you write to it seems slightly useless, at least in my opinion.

Lol, you are correct. Writing value X to $5209 causes interrupt to trigger on X-th rising edge of M2. Because M2 needs to be toggled constantly, I did not realise that before. And writing value 0 never triggers interrupt, probably because it is triggered when counter clockes from 1 to 0.

Though, only 8 bit M2 counter seems to be hardly useful. I wonder where to write high byte

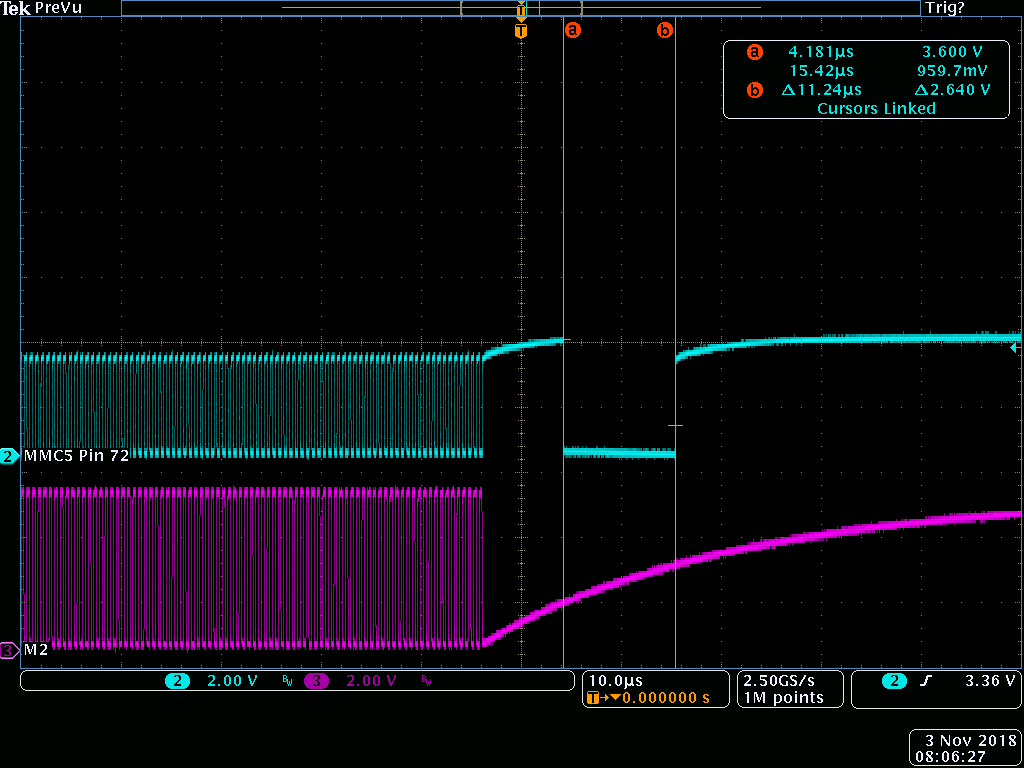

Also, when M2 stops toggling, around 11us from that time MMC5 is bring to reset (causing interrupt line to go high)

Coooool! That is a super nice feature that nobody knew about! You could use that timer interrupt to write raw DAC samples!! That discovery is GOLDEN

My setup can't toggle M2 that fast so I would not have been able to test this. Did you try writing anything to $520A? In keeping with the multiplier result being in little endian, it seems that the high byte (if existing) might come after the low byte for this too.

Edit:

Additional questions about this register while the timer is running, before the IRQ happens (ex. writing a big value like $FF so you have time to try stuff):

- What happens if you read register $5209? Is there a different flag to show that it is running?

- How about reading register $5208 while it is running? Is it still reporting $C0?

- What happens if you write value $01 - will it reload the counter and have the IRQ next rising edge of M2, or continue counting from the original value you wrote?

- What happens if you write value $00 - does it cancel the timer and never generate the IRQ?

If it matters, I seem to remember there being multiplication algorithms that generate 2 bits per iteration. Multiplying two 8-bit numbers would converge in 4 iterations, which at 1 cycle per iteration is the time from a write to the following read.

I think that does matter tepples -- that method could save a lot of resources when trying to replicate MMC5 in hardware.

I was not able to ever observe an incomplete product, but I was testing extremely slow and I was toggling M2 during the test, which I am not sure is necessary or not. I didn't try it without toggling M2. Since, to your point, the NES could not possibly expect to read the result until some cycles later, it definitely seems reasonable to implement a multiply that relies on that fact -- whether or not a real MMC5 technically does it faster.

Quote:

What happens if you read register $5209? Is there a different flag to show that it is running?

It read backs as $00. After the X-th edge it read backs as $80 (and reading it clears pending interrupt).

Interrupt is reported around 41ns after rising edge of M2 and it is cleared also around 41ns after falling edge of M2 of the "read $5209" cycle.

If the X-th cycle is "read $5209" then the interrupt is reported only for the period of time between rising and falling edge (as below).

And it counts M2 cycles (no matter if this is read or write cycle)

Quote:

How about reading register $5208 while it is running? Is it still reporting $C0?

Yes, before/on/after X-th edge it is still $C0

Quote:

What happens if you write value $01 - will it reload the counter and have the IRQ next rising edge of M2, or continue counting from the original value you wrote?

IRQ will be triggered on the next rising edge of M2

Quote:

What happens if you write value $00 - does it cancel the timer and never generate the IRQ?

Yes. But if the IRQ is already pending, writing $00 to $5209 does not cause it to acknowledge.

And yes, $520A is used to write upper 8 bits of the counter.

And no, $520B is not upper 16-23 bits (counter is only 16 bits wide)

krzysiobal wrote:

And yes, $520A is used to write upper 8 bits of the counter.

Do writes to $5209 start the counter, then? Or does it just count while nonzero, and certain values are harder to request?

krzysiobal wrote:

And yes, $520A is used to write upper 8 bits of the counter.

And no, $520B is not upper 16-23 bits (counter is only 16 bits wide)

Great work!!

krzysiobal wrote:

And yes, $520A is used to write upper 8 bits of the counter.

And no, $520B is not upper 16-23 bits (counter is only 16 bits wide)

Presumably, writing $01 to $520A and then $00 to $5209 will generate an IRQ after exactly 256 cycles.

Next things to figure out:

1. Does it matter in what order you write the values to $5209-$520A? (i.e. will the sequence $01 -> $520A, $80 -> $5209, $02 -> $520A trigger an IRQ after 384 cycles or after 640 cycles?)

2. What exactly, then, is at $5207-$5208?

lidnariq wrote:

krzysiobal wrote:

And yes, $520A is used to write upper 8 bits of the counter.

Do writes to $5209 start the counter, then? Or does it just count while nonzero, and certain values are harder to request?

It seems that only writing to $5209 starts the counter. That is, the following sequence:

write($5209, 0)

write($520A, 0)

write($520A, 1)

will not start counter, but the one below will:

write($5209, 0)

write($520A, 0)

write($520A, 1)

write($5209, 0)

Also, when the counter is ticking, writing to $520A will cause its value to be modified so there are no temporary registers:

write($5209, $5)

write($520A, $1)

write($520A, $ff) <- it will immediatelly update counter high byte

I did a not-so-exciting test on $5207 / $5208 last night. I wrote all possible combinations of data to registers $5207 and $5208 and I didn't read anything other than $C0 from $5208 from the entire test.

It went like this:

Code:

Init:

R/W = 1 (read from MMC5)

M2 = 1 (allow reading and loading new data)

for( int i = 0x0000, i <= 0xFFFF, i++ )

{

// Write low byte of i to $5207

Record low byte of i to spreadsheet

CPU address = $5207

R/W = 0 (write to MMC5)

Set logic analyzer to output to CPU data bus

Set data bus to low byte of i

M2 = 0 (register the data)

M2 = 1 (allow reading and loading new data)

// Read back register $5208

Set logic analyzer to input from CPU data bus

R/W = 1 (read from MMC5)

Record data bus value to spreadsheet

// Write high byte of i to $5208

Record high byte of i to spreadsheet

CPU address already = $5208, no action

R/W = 0 (write to MMC5)

Set logic analyzer to output to CPU data bus

Set data bus to high byte of i

M2 = 0 (register the data)

M2 = 1 (allow reading and loading new data)

// Read back register $5208

Set logic analyzer to input from CPU data bus

R/W = 1 (read from MMC5)

Record data bus value to spreadsheet

}

Edit:

Running the same test again but now reading register $5206 each time. If any combination of values written to $5207 / 5208 should turn the multiply into a signed multiply, $5206 should become $00 instead of $FE.

$FF(unsigned: 255) * $FF(unsigned: 255) = $

FE01(unsigned: 65025)

$FF(signed: -1) * $FF(signed: -1) = $

0001(signed: 1)

Seems doubtful but worth a try.

Edit 2:

Result: $5206 was always $FE during every step of that test. We can probably say that no combination of inputs to the multiplier affect the readback value of $5208, and no combination of inputs written to registers $5207 or 5208 affect the result of the multiplier.

Out of curiosity, have you tried just generically fuzzing the MMC5? Write random values randomly all over the $5000-$52FF range and see if $5208 changes?

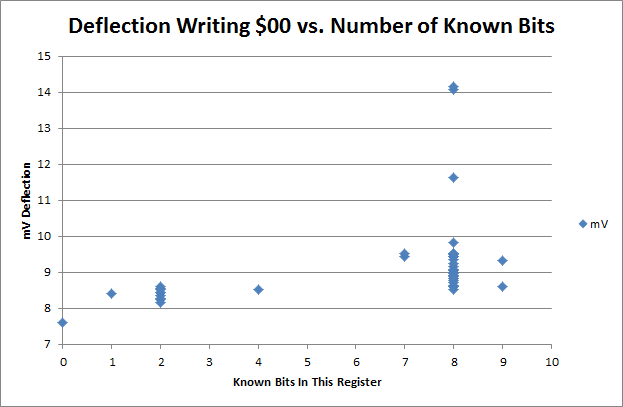

I don't know why but I have a premonition that $5208's value might be in connection to some hardware aspect of chip:

* How MMC5 is wired (SL/CL mode)

* Voltage of the battery (pin 57)

* Revision

lidnariq wrote:

Out of curiosity, have you tried just generically fuzzing the MMC5? Write random values randomly all over the $5000-$52FF range and see if $5208 changes?

Great idea, I will try it.

krzysiobal wrote:

I don't know why but I have a premonition that $5208's value might be in connection to some hardware aspect of chip:

* How MMC5 is wired (SL/CL mode)

* Voltage of the battery (pin 57)

* Revision

Cool theories. For the idea of revision, it seems that both of us have chips marked MMC5A. Do you have any other MMC5 carts that might have the non-A version? I will dig a bit but I am almost sure I do not have any others.

My setup has battery removed. Do you still have the battery installed in yours?

My setup has SL/CL disconnected. Are yours connected?

I have an MMC5letterless cart, but no testing apparatus.

Do you have a ROM dumper? $5208 should be easily dumpable.

In other news, it seems there is some sort of locking function. At the beginning of my test, bankswitching of CHR was occurring quite frequently with random writes to random addresses in the range $5000-$52FF, then all of a sudden it got stuck and has remained stuck for a long time now. I think I will let it go and see if it will unstick itself by morning - could be interesting. Maybe the MMC5A "crashed" somehow, that would have interesting implications to consider if it is crashable. Hopefully it doesn't have firmware in there that I just wiped out. That seems pretty doubtful for the mid 1990s I guess but you never know.

I plan to review the data between the last successful bankswitch and the next time that it should have done a bankswitch, and see what happened between there. As of yet, I have seen no changes to the unknown pins or to register $5208.

Edit:

I gave in and power cycled the MMC5 and restarted the test. It functions normally again, but it does seem to lock up quite quickly from this test. I might try playing with the random address range written to and see if I can narrow down any particular addresses that cause this locking. In both lock-ups, it ended up with CHR address pointing thusly: CHR A19 and A18 = 0. CHR A17 to A10, A2 to A0, CL3, SL3, all equal 1. PRG A19 to A13 all equal 1 (not sure they ever changed though to begin with though). Definitely no changes to the unknown pins in this test. They all remained either driven high or hi-z (can't currently tell the difference).

Edit 2:

Changing my random address range to be $5120 to $512B, it locked up almost immediately. Reducing the range to $5120 to $512A allowed the PPU bank to keep dancing all over indefinitely. So, writing to $512B can cause the lockup of the PPU bank. Maybe it is waiting for additional PPU reads, etc - I am not familiar with this.

Then, specifically excluding $512B from address range $5000 to $52FF, it still was able to lock up. I then excluded the range $512B to $512F, and now it does not lock up. Therefore, there is at least 1 more register in that range that behaves similar to $512B. The test is now set up to run all night, avoiding this address range. I should have a million or so random writes and dumps of all pins by morning.

Edit 3:

Lidnariq: I went ahead and ordered up 2 cheap Famicom L'Empereurs, hopefully one of them will have a non-'A' MMC5.

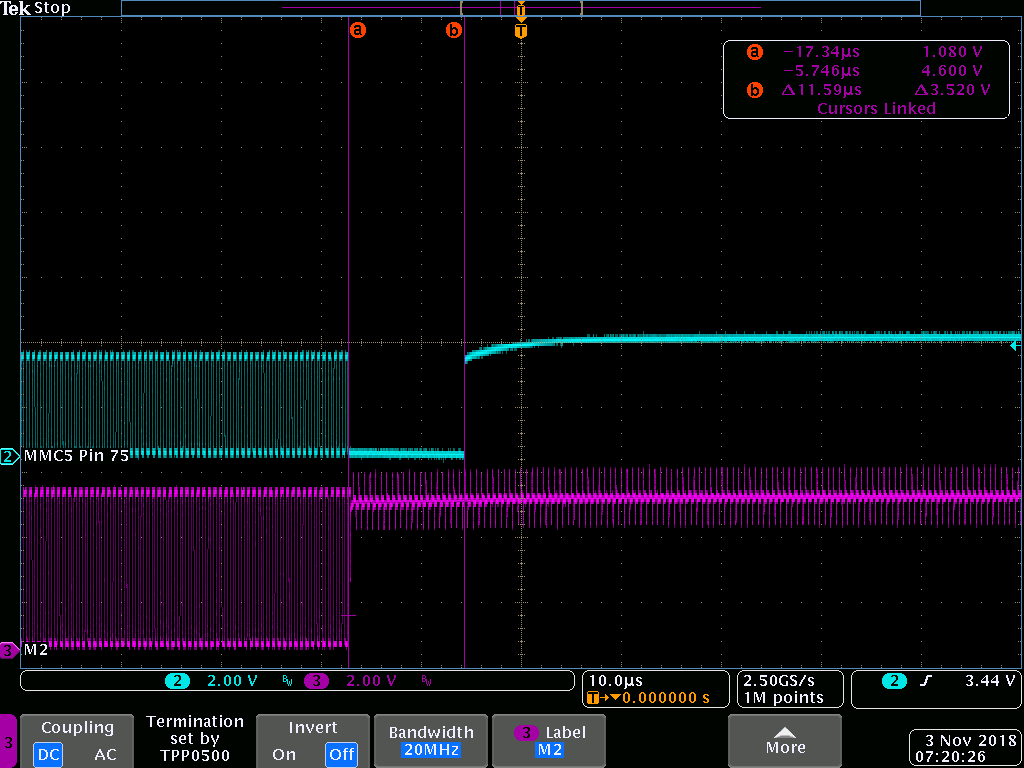

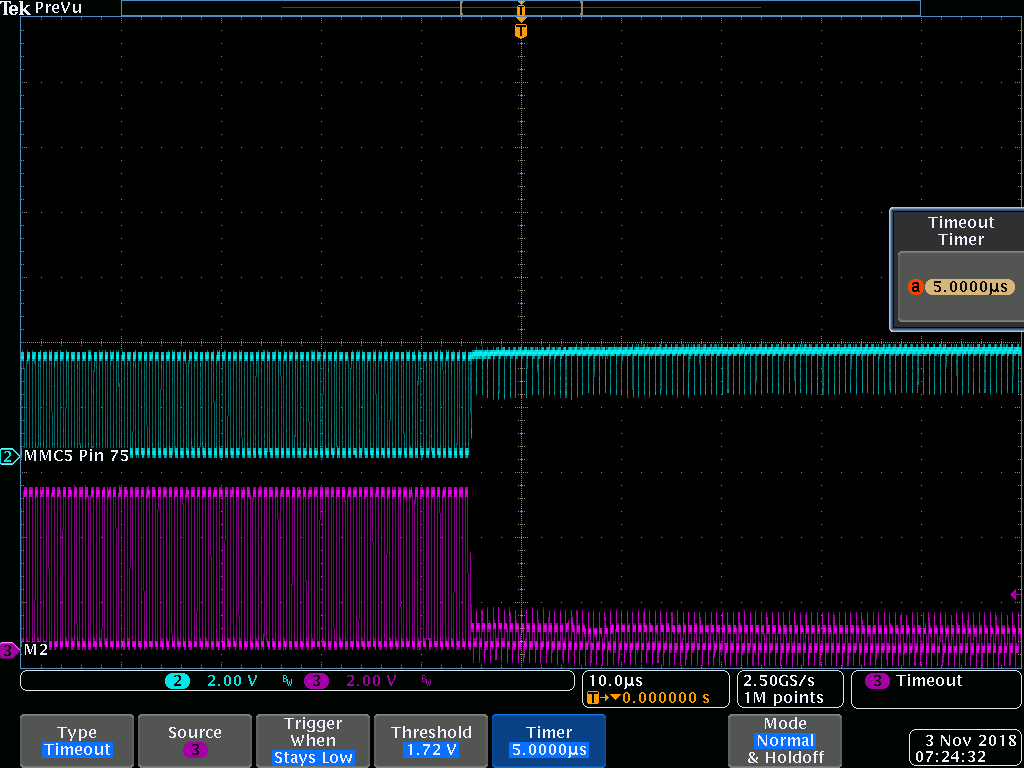

You should make all addres line / RnW changeswhen M2 is 0 and put M2 to 0 after end of cycle, otherwise you are risking doing extra read/write cycles. Unfortunatelly from the code example, you are doing the opposite.

Maybe when M2 stops cycling, also all of its banking settings does to default?

---

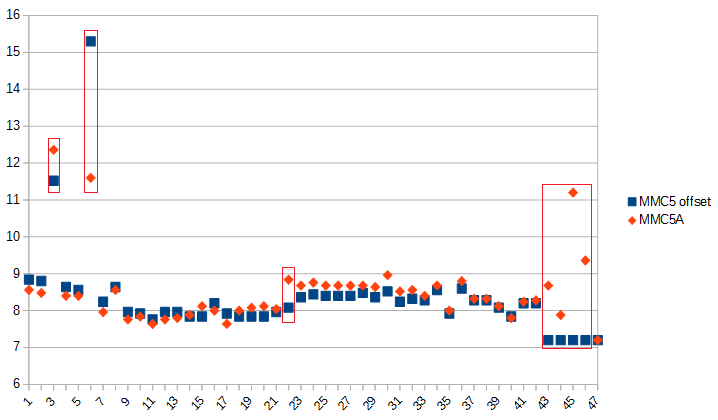

All the test were done without battery, but when I plug battry into the socket, nothing changed concerning $5208.

---

BINGO! I still does not know the role of pin 98 and 97 (if that switches between CL and SL mode, why there is just not one input pin that connects between VCC and GND?).

Nevermind, I cut the CL3 jumper (which connected MMC5.98 with MMC5.97). Now both of them are not connected to anything. Reads of $5208 still returns C0.

But both of the pins seems to be inputs (with pullups to VCC). When both of them are not connected to anything, there is 5V on them, but after shorting any of them to GND (with even weak serial 4.7k resistor, the voltage drops to ~0.2V, so they must be inputs)

Shorting any of them to GND alters the value returned by $5208:

Code:

[AB00 0000] $5208 (reading)

||

|+---------- value of MMC5.97 pin

+----------- value of MMC5.98 pin

Now there need to be figured out:

* Does changing vale of those pins alters any MMC5 behaviour or

* are just they some kind of DIP swithes that game can readback (like in MAPPER90 games)

Wiki says that:

Quote:

In other words, CL mode passes the lowest PPU address bits straight to CHR ROM, while SL mode runs them through MMC5. SL mode allows the MMC5 to perform smooth vertical scrolling in split mode, while CL mode does not. Nearly all MMC5 cartridges use CL mode - it is not known why SL mode was not used instead: possibly ROM speed issues.

But I analyzed all the MMC5 PCBs from botgod and no single one uses SL mode.

Oh cool - I am glad you were able to figure that out, and thanks for sacrificing your CL3 jumper.

I genuinely did not know that the right time to make address changes was when M2 is 0. I will do that from now on.

It looks like the CHR banking is not reset from stopping M2 toggling. Since my PPU address bus is just floating, which ends up all 1s, I am not getting a very good representation of the actual banking that is going on, but the extended CHR address bits do flip one way, stay for a while, flip the other way, stay for a while, during this test. If it was resetting, I think it would mostly stay the same, and show little glitches as it changed and reset back right away.

I never did witness the PRG banking change (haven't checked the results this morning yet), so it makes sense that one is reset by delay in M2. I would probably not have seen the said glitches on the extended PRG bits unless I had my scope hooked to them or something.

Edit:

krzysiobal wrote:

Wiki says that:

Quote:

In other words, CL mode passes the lowest PPU address bits straight to CHR ROM, while SL mode runs them through MMC5. SL mode allows the MMC5 to perform smooth vertical scrolling in split mode, while CL mode does not. Nearly all MMC5 cartridges use CL mode - it is not known why SL mode was not used instead: possibly ROM speed issues.

But I analyzed all the MMC5 PCBs from botgod and no single one uses SL mode.

The wiki also said that there are 2 versions of MMC5: "MMC5" and "MMC5B". I think we have some work to do on the wiki. As we find things that seem somewhat conclusive, I have been (and I will continue to) add them on there as we go.

I will play around with CHR address ranges and see if I can affect either of these pins. They could be bi-directional pins. It seems quite odd to connect together 2 inputs, and not connecting them to gnd or vcc. There must be something more to that.

Edit 2:

In summary of the test, the only pins that ever changed after over 1,000,000 writes were the bankswitched CHR address bits. None of the unknown pins, and none of the PRG address bits. I had all PPU address bits = 1 the whole time.

The CPU address bits were being controlled to do the writes and reads, and at the time of sampling these bits, the CPU address would always have been $5208.

Looking at the writes in the range $5120 to $512A that caused a CHR bankswitch:

Code:

Range $5120 - 5127:

A19 A10 SL3 CL3 A2 A0

| | | | | |

0011 1111 11 1 1 111

Range $5128 - 512A

A19 A10 SL3 CL3 A2 A0

| | | | | |

0000 0000 00 1 1 111

I got a reasonably even distribution of writes that triggered the change of A17 through A10, also really even distribution of the value that was written. I did observe one single write of $00 that triggered a bankswitch, but my test observed no write of value $FF that triggered it. It is completely possible that the random test just never hit that combination.

5120: 31

5121: 21

5122: 28

5123: 25

5124: 23

5125: 17

5126: 19

5127: 21

5128: 70

5129: 58

512A: 56

Ben Boldt wrote:

krzysiobal wrote:

But I analyzed all the MMC5 PCBs from botgod and no single one uses SL mode.

The wiki also said that there are 2 versions of MMC5: "MMC5" and "MMC5B".

Nah, we know that there are a very finite number of PCBs that used the MMC5 and all four of them per region left it in CL mode.

If there were dedicated prototyping boards made for the MMC5 (ETPROM?) maybe those support it. But we haven't found any yet.

The CL/SL mode stuff has been on the MMC5 pinout wiki page since its creation by user

Banshaku in 2009. Are you around for comment Banshaku?

I tried putting a 10k pull-down on each of the unknown pins, and I found the following voltage clues:

- VCC 5.01V

- Pin#, Open Voltage, 10k to Gnd voltage

- 94 (CHR A0), 5.01, 4.96 <- Clearly driven high

- 74 (PRG /CE), 5.01, 4.97 <- Clearly driven high

- 70 (PRG RAM A14), 5.01, 4.97 <- Clearly driven high

- 73 (unknown), 5.01, 4.97 <- Clearly driven high

- 93 (unknown), 5.01, 4.96 <- Clearly driven high

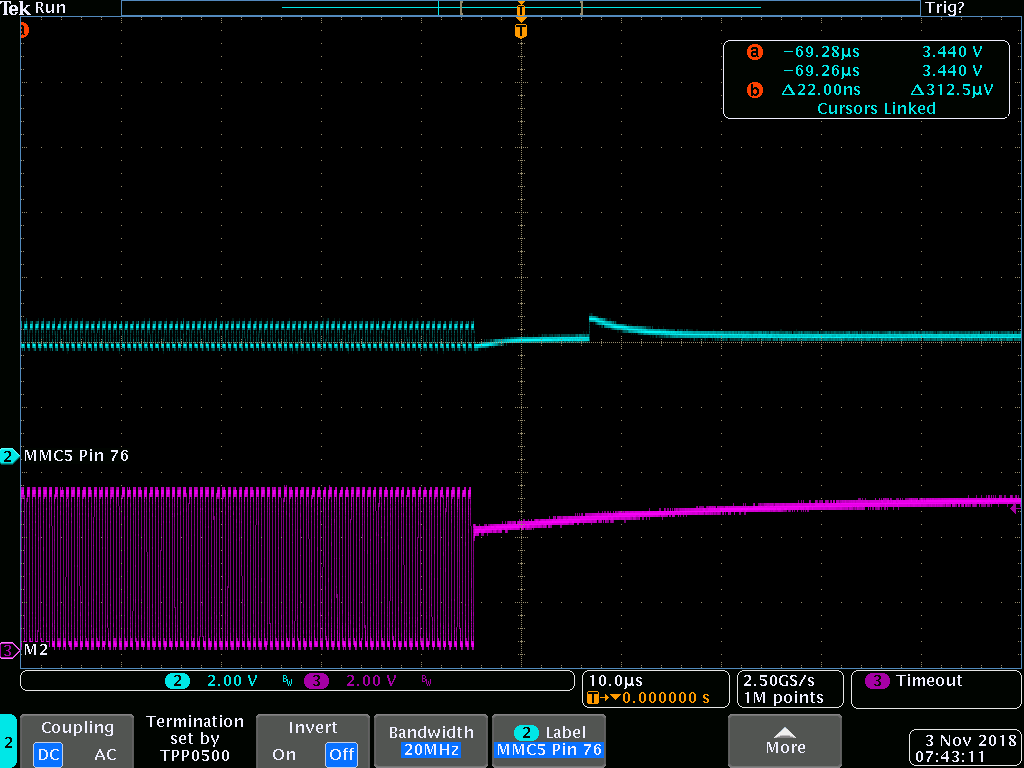

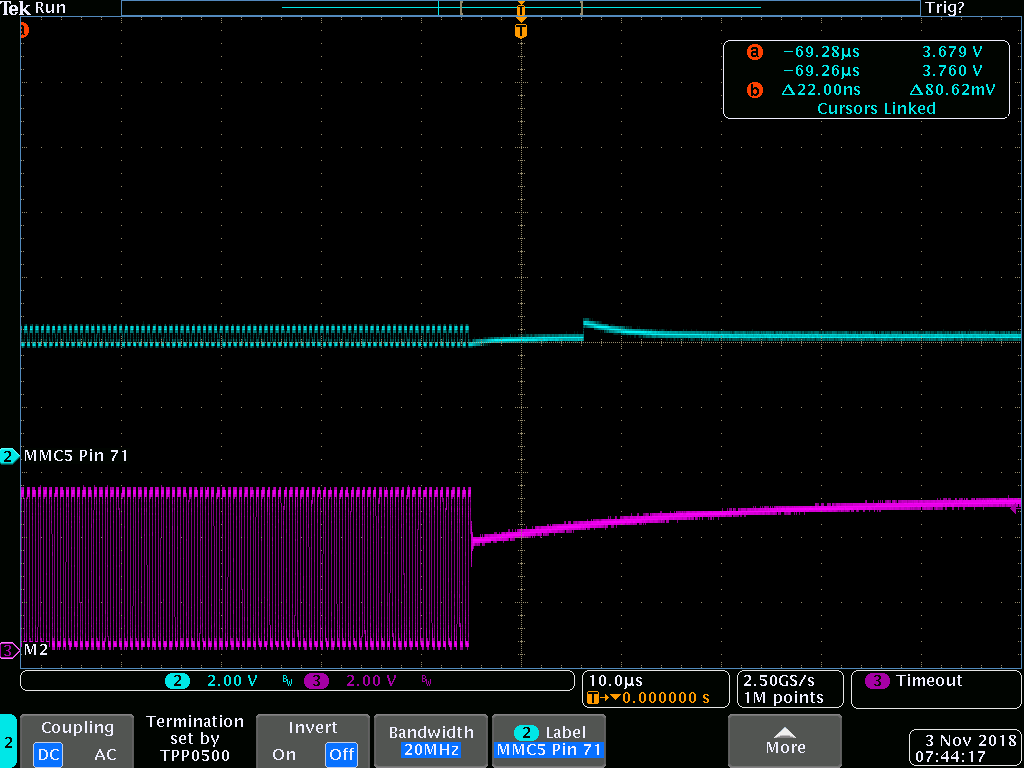

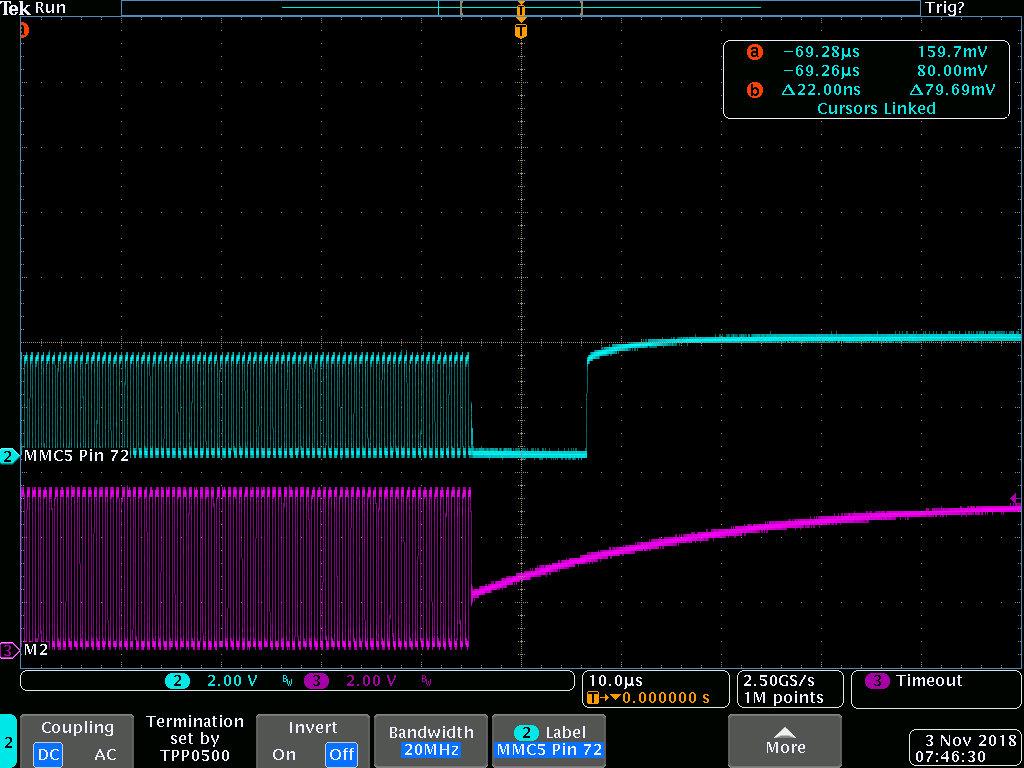

- 76 (PRG RAM /WE) 4.96, 3.17

- 72 (PRG RAM 1 /CE), 4.96, 3.17

- 71 (PRG RAM 0 /CE), 4.96, 3.17

- 75 (unknown), 4.96, 3.17

- 30 (unknown), 5.00, 1.94

- 29 (unknown), 5.00, 1.93

- 92 (unknown), 5.00, 1.86

- 82 (unknown), 5.00, 1.85

- 81 (unknown), 5.00, 1.72

- 28 (PPU A13), 4.96, 0.89 <- Input

- 98 (SL3), 4.99, 0.90V <- Input

- 97 (CL3), 4.99, 0.90V <- Input

Edit:

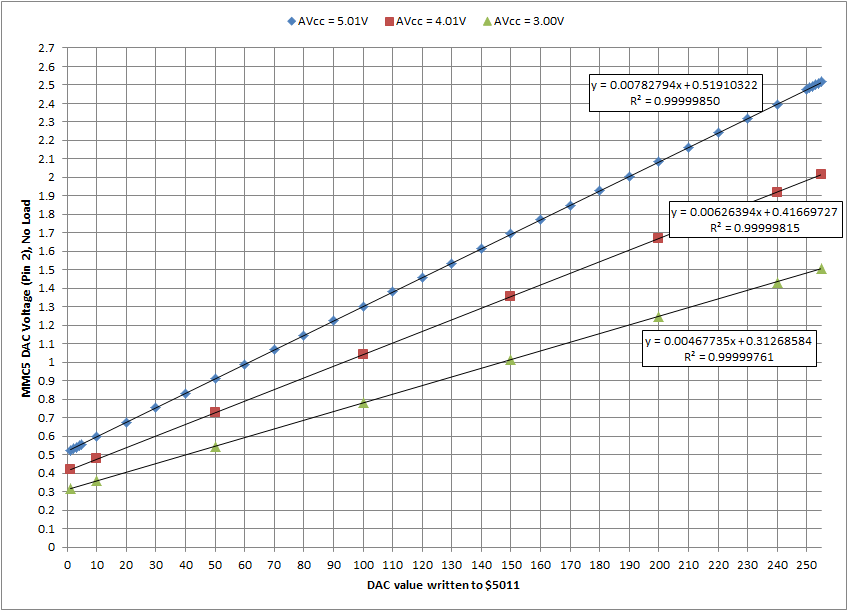

verified that DAC is indeed coming out from Pin 2. I characterized the voltage to DAC value here:

https://wiki.nesdev.com/w/index.php/MMC ... .245011.29

Ben Boldt wrote:

The CL/SL mode stuff has been on the MMC5 pinout wiki page since its creation

It was just copied from kevtris's documentation

here.

lidnariq wrote:

Ben Boldt wrote:

The CL/SL mode stuff has been on the MMC5 pinout wiki page since its creation

It was just copied from kevtris's documentation

here.

Okay. Where do you think he got that info from? How would he know that it has to do with split-screen scrolling? To me, looking at Just Breed's PCB, all of the jumpers that are closed are labeled CLx and all of them that are open are labeled SLx (where x is a number). It looks like for each x, there is a pair of CLx and SLx always near each other. If CL and SL are to be overall modes of the MMC5, it might shed some light to think about the overall differences when opening all of the CLx and closing all of the SLx -- not just CL3 and SL3.

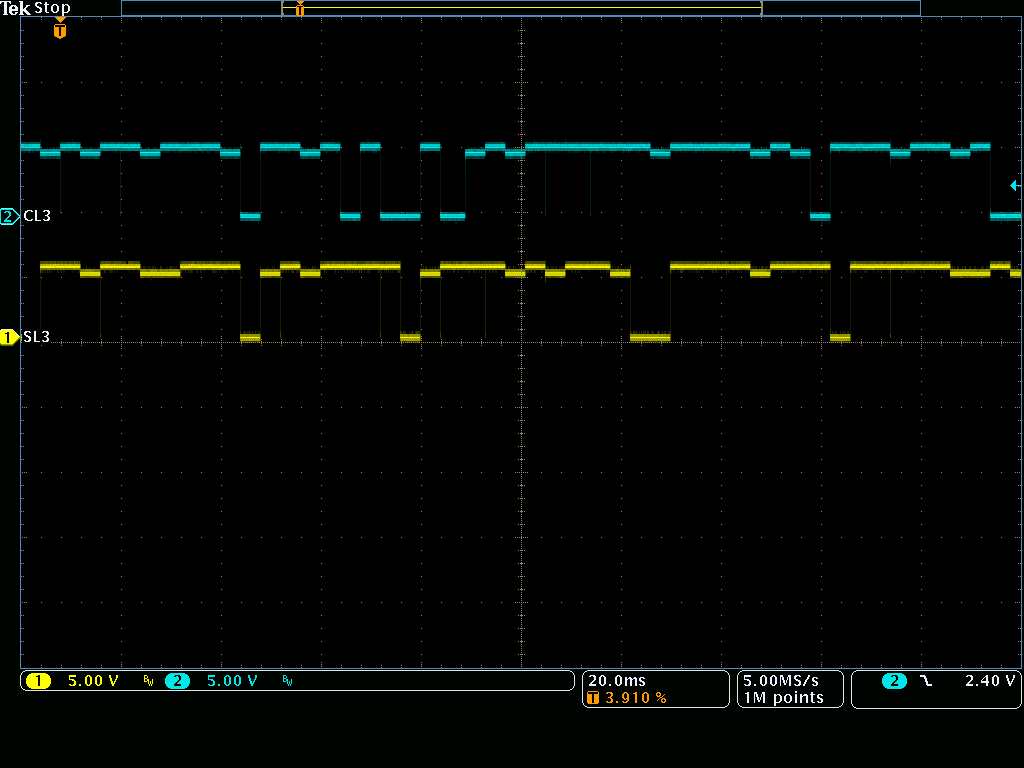

Well, we know by inspection that CL4-6 and SL4-6 connect CHR A0-A2 to PPU A0-A2, or instead go via the MMC5.

And the only known behavior that could use that is the left-and-right split screen. (Or flipping background tiles vertically, but that's evidently not present)

Similarly, we know what SL2/CL2 (battery backup of RAM), SL1/CL1 (battery backup of second RAM), and SL15/CL15 (enables two 32KiB RAMs on NES-ETROM) do.

As to whether Kevtris assumed something, or was citing some even older source ... don't know. You might be able to get in touch with him via IRC.

lidnariq wrote:

And the only known behavior that could use that is the left-and-right split screen.

Okay, that explains a lot. I admittedly had not even looked at where any of the jumpers connect yet, but I would not have been able to see the relation to split screen anyway. Thanks for your experience on this. So basically, swapping several CLx/SLx pairs appears to be the idea kevtris was already going on, possibly with the same assumptions that I was suggesting.

I guess the pins named CL3 and SL3 are right next to CHR A0, A1, A2, and these 3 address bits point to the split screen business. That does seem a pretty strong indication that they are directly related. In case they aren't, it is easy for me not to get stuck on that relation because I don't understand it anyway!

I research it with a truly open mind.

Ben Boldt wrote:

I guess the pins named CL3 and SL3 are right next to CHR A0, A1, A2, and these 3 address bits point to the split screen business. That does seem a pretty strong indication that they are directly related. In case they aren't, it is easy for me not to get stuck on that relation because I don't understand it anyway!

Unfortunately, they're not. (Much to my disappointment/surprise)

4-6 are vaguely in the middle of the PCB, between CHR and the MMC5.

1 and 2 are next to their corresponding PRG RAM

15 isn't particularly near anything, between PRG ROM and PRG RAM

but 3 is off in the corner near the battery in HVC/NES-E{K/T/W}ROM.

HVC/NES-ELROM might be the exception that led to the impression. On these PCBs 3 is vaguely near 4-6.

I think I would like to set up a test that has random PPU addresses, writes and reads, and monitors CHR A0, A1, A2, CL3, SL3, and especially Unknown Pin 93.

I measured the voltages of all pins today with and without a 10k pull-down. Only PRG RAM /CE /WE -related pins do the 3.17V thing measured on pin 75. That is a good clue that 75 relates to those.

73 and 93 act like ordinary output high seen on lots of pins. Our best clues are proximity to other pins. 73 measures like 74 (PRG /CE), also 93 measures like 94/95/96 (CHR A0/A1/A2).

Pins 29, 30, 81, 82, and 92 all have this weird 1.8V business not seen on any known pins.

It works out to an 18k internal pull-up. It could mean that those pins are related to each other, or it might not be a good sign that those pins actually do anything... But at least 73/75/93 look promising.

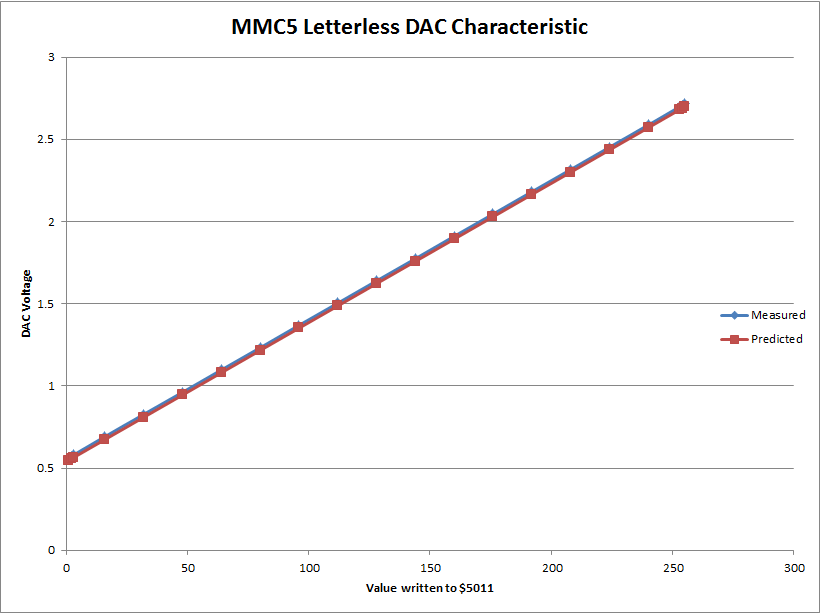

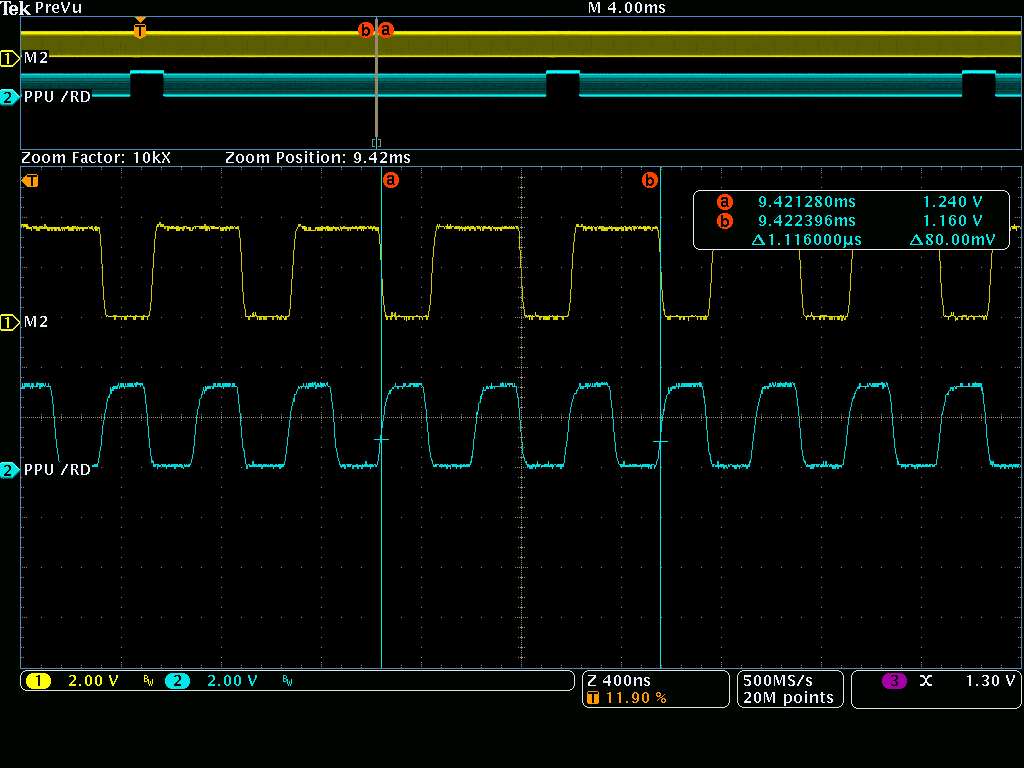

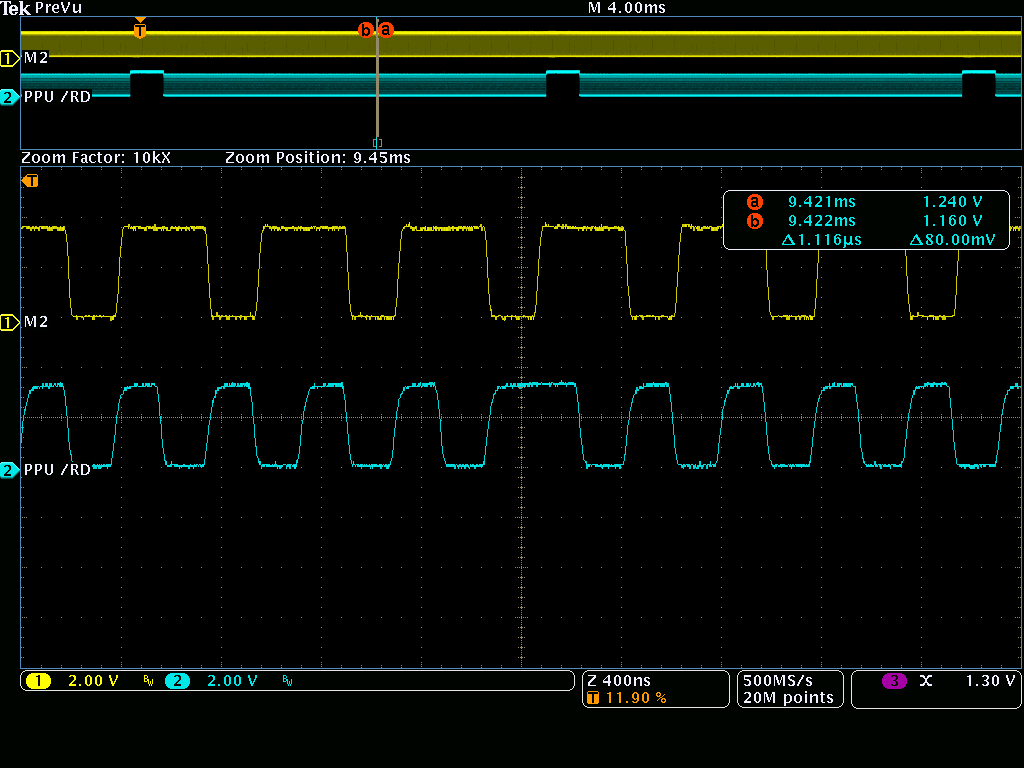

I did some more DAC testing and came up with a more general equation that considers AVcc:

Pin 2 Voltage = [(DAC value / 255) * (0.4 * AVcc)] + (0.1 * AVcc)

Attachment:

dac characteristic.png [ 38.98 KiB | Viewed 2690 times ]

dac characteristic.png [ 38.98 KiB | Viewed 2690 times ]

I updated the

Wiki with this.

I keep dreaming about the DAC being able to play by itself out of the MMC5's internal RAM, and then interrupt when done. That would be so cool.

If you leave AVcc floating, but supply +5V on DVcc, what voltage appears on AVcc?

lidnariq wrote:

If you leave AVcc floating, but supply +5V on DVcc, what voltage appears on AVcc?

And try to measure the internal resistance of that output too.

lidnariq wrote:

If you leave AVcc floating, but supply +5V on DVcc, what voltage appears on AVcc?

Flat zero.

krzysiobal wrote:

And try to measure the internal resistance of that output too.

Will do. DACs typically are made out of big resistor networks so I will consider that and test different conditions, etc.

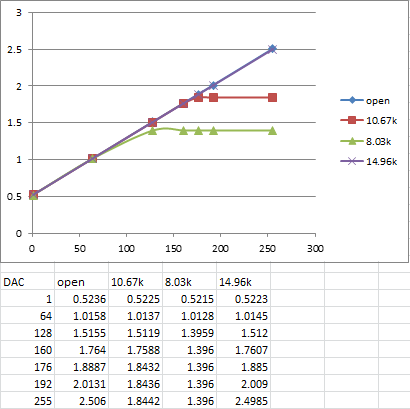

Edit:

It looks to have a current-limited output at about 173 uA:

Attachment:

dac impedance.png [ 14.38 KiB | Viewed 2664 times ]

dac impedance.png [ 14.38 KiB | Viewed 2664 times ]

I calculate the maximum non-distorted load to be 14.45 kohm to gnd. I am not sure if it hurts it to enter current-limit mode, so I only applied the load momentarily for each point to read the meter, then took it away.

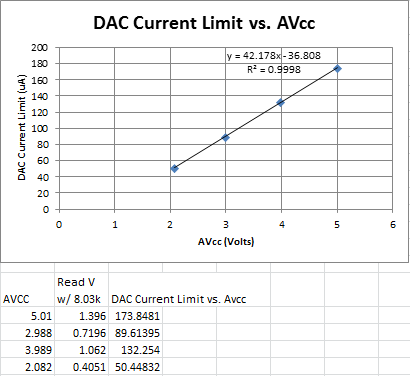

Edit 2:

I have more work to do on this -- The current limit depends on AVcc. The graph shown is with AVcc = 5V. I tried reducing AVcc to 3V and it current limited to 0.720 volts with the 8.03k resistor.

Edit 3:

Attachment:

dac current limit vs. AVcc.png [ 13.21 KiB | Viewed 2663 times ]

dac current limit vs. AVcc.png [ 13.21 KiB | Viewed 2663 times ]

Wait, so the MMC5 DAC is linear? That means it's not just a repackaged APU.

Do you have any plans to measure the pulse channels? I'm not hardware-savvy enough to tell if that's feasible with your setup.

Rahsennor wrote:

Wait, so the MMC5 DAC is linear? That means it's not just a repackaged APU.

We've known for a long time that the MMC5's pulse channels aren't just a repackaged APU, and the presence of a linear DAC would just be

one of the reasons. Another would be the lack of pitch sweeping support (which isn't surprising, because they took up about 1/3 of the RP2A03 pulse channels' die space), and yet another would be the fact that the RP2A03 and MMC5 use inherently different processes (the former is depletion-load NMOS, while the latter is CMOS).

Still, replacing the DAC would've been trivial even if the MMC5

did use a direct copy of the NES APU, since it's only a single isolated component of it - in

Visual 2A03, the Pulse DAC is just the region enclosed by t10283 and t10311, and the Triangle/Noise/PCM DAC is just the area within t13792 and t14502.

Quietust wrote:

MMC5 use inherently different processes [...] while the latter is CMOS

We know it's CMOS?

lidnariq wrote:

Quietust wrote:

MMC5 use inherently different processes [...] while the latter is CMOS

We know it's CMOS?

I suppose we technically don't know 100% for certain, so I retract that particular statement.

Do we have any insinuation that it's CMOS?

I assumed it was NMOS because inputs source current, so if there's any evidence any direction I'm curious to hear about it.

Rahsennor wrote:

Wait, so the MMC5 DAC is linear? That means it's not just a repackaged APU.

Do you have any plans to measure the pulse channels? I'm not hardware-savvy enough to tell if that's feasible with your setup.

I could try that. I am thinking that the M2 reset detection would probably stop the pulse channels, so as to prevent stuck notes when you reset the Nintendo, so that might be a problem with my setup. I might try using a function generator into M2 to get around this.

I am not quite set up for fast M2 yet, I have to think about it a little bit more and get that going before I can look at the pulse channels. In the meantime, I tried writing to the MMC5's built-in RAM. Something isn't working right. I always read back all 00s from the RAM. Could you guys review my test code and let me know anything you notice? Especially consider how I am handling M2 and R/W edges - I don't have a good handle on the correct sequence of those yet. Are there more modes I need to set or unlocks that I need to do? Or could my slow M2 be screwing this up somehow? Hopefully not.

Code:

private void testFillRam()

{

byte data_to_write = 0x10;

string s = "";

readAndRefreshGraphics();

// Set CPU R/W, /ROMSEL, and M2 as outputs:

sendDataDirection(0xF8, 0x4A, 0);

// Set these outputs to high:

setCpuRW(true);

setRomSel(true);

setM2(false);

// Send

sendOutput(logicData[5][0], 0x4A, 0);

// Set CPU address bus as output:

sendDataDirection(0x00, 0x42, 0);

sendDataDirection(0x00, 0x42, 1);

setCpuRW(false);

sendOutput(logicData[5][0], 0x4A, 0);

// Set CPU data bus as output:

sendDataDirection(0x00, 0x46, 0);

// Write value $02 to register $5102:

setCpuAddress(0x5102);

sendOutput(logicData[1][0], 0x42, 0); // LSB

sendOutput(logicData[1][1], 0x42, 1); // MSB

logicData[3][0] = 0x02; // Data to write

sendOutput(logicData[3][0], 0x46, 0);

setM2(true); // Register the data

sendOutput(logicData[5][0], 0x4A, 0);

setM2(false);

sendOutput(logicData[5][0], 0x4A, 0);

// End set $5102 to unlock value $02:

// Write value $01 to register $5103:

setCpuAddress(0x5103);

sendOutput(logicData[1][0], 0x42, 0); // LSB

sendOutput(logicData[1][1], 0x42, 1); // MSB

logicData[3][0] = 0x01; // Data to write

sendOutput(logicData[3][0], 0x46, 0);

setM2(true); // Register the data

sendOutput(logicData[5][0], 0x4A, 0);

setM2(false);

sendOutput(logicData[5][0], 0x4A, 0);

// End set $5103 to unlock value $01:

// Write mode value $02 to register $5104:

setCpuAddress(0x5104);

sendOutput(logicData[1][0], 0x42, 0); // LSB

sendOutput(logicData[1][1], 0x42, 1); // MSB

logicData[3][0] = 0x02; // Data to write

sendOutput(logicData[3][0], 0x46, 0);

setM2(true); // Register the data

sendOutput(logicData[5][0], 0x4A, 0);

setM2(false);

sendOutput(logicData[5][0], 0x4A, 0);

// End set $5104 to mode 02 (normal RAM)

// Start: write non-zero, non-FF, non-negative data to entire expansion RAM:

for (int i = 0x5C00; i < 0x6000; i++)

{

setCpuAddress((UInt16)i);

sendOutput(logicData[1][0], 0x42, 0); // LSB

sendOutput(logicData[1][1], 0x42, 1); // MSB

logicData[3][0] = data_to_write; // Data to write

sendOutput(logicData[3][0], 0x46, 0);