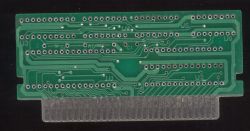

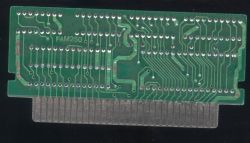

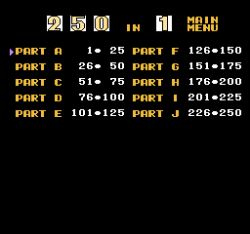

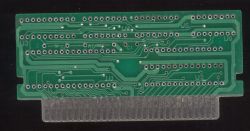

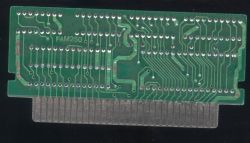

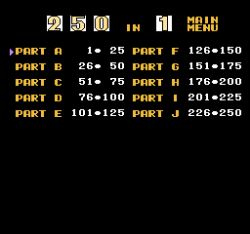

I found interesting multicart 250-in-1. It is quite similar to known Contra 168-in-1/100-in 1 (Mapper 015):

* consists of UNROM/NROM-256/NROM-128 games,

* some of games were hacked so that it is possible to change starting level or number lifes,

* after restart, menu shows the position at which last game was selected (probabl it is stored on $1ff and every game

was hacked so that its stack is pointing at $1fe),

* mapper is REALLY similar to mapper 15 but it reacts only to writes on $f000-ffff:

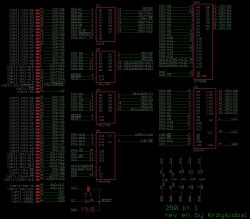

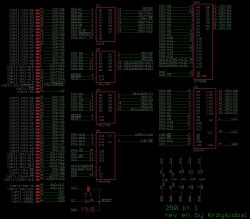

Pal equations:

* consists of UNROM/NROM-256/NROM-128 games,

* some of games were hacked so that it is possible to change starting level or number lifes,

* after restart, menu shows the position at which last game was selected (probabl it is stored on $1ff and every game

was hacked so that its stack is pointing at $1fe),

* mapper is REALLY similar to mapper 15 but it reacts only to writes on $f000-ffff:

Code:

A~[1111 .... .... wMMM] D~[amPPPbcd] Main register: $f000-$ffff (cleared on powerup & reset)

|||| ||||||||

|||| +||||+++---- inner PRG bank (real configuration depends on mode)

|||| |+++------- outer PRG bank (PRG_A19..17)

|||| +---------- mirroring (0=V, 1=H)

|+++----------------- mode

+-------------------- CHR-RAM write protection (1=enabled)

A2 A1 A0 D7 D2 D1 D0 | $6000-$7fff | $8000-$9fff | $a000-$bfff | $c000-$dfff | $e000-$ffff | comment

* 0 0 * b c * | open bus | PPPbc00 | PPPbc01 | PPPbc10 | PPPbc11 | NROM-256

0 0 1 * b c d | open bus | PPPbcd0 | PPPbcd1 | PPP1110 | PPP1111 | UNROM

* 1 0 a b c d | open bus | PPPbcda | PPPbcda | PPPbcda | PPPbcda | 8kB (accessing CHR data)

* 1 1 * b c d | open bus | PPPbcd0 | PPPbcd1 | PPPbcd0 | PPPbcd1 | NROM-128

1 0 1 * * * * | PPPbcda | PPP1100 | PPP1101 | PPP1110 | PPP1111 | $6000 + last 32 kB

|||| ||||||||

|||| +||||+++---- inner PRG bank (real configuration depends on mode)

|||| |+++------- outer PRG bank (PRG_A19..17)

|||| +---------- mirroring (0=V, 1=H)

|+++----------------- mode

+-------------------- CHR-RAM write protection (1=enabled)

A2 A1 A0 D7 D2 D1 D0 | $6000-$7fff | $8000-$9fff | $a000-$bfff | $c000-$dfff | $e000-$ffff | comment

* 0 0 * b c * | open bus | PPPbc00 | PPPbc01 | PPPbc10 | PPPbc11 | NROM-256

0 0 1 * b c d | open bus | PPPbcd0 | PPPbcd1 | PPP1110 | PPP1111 | UNROM

* 1 0 a b c d | open bus | PPPbcda | PPPbcda | PPPbcda | PPPbcda | 8kB (accessing CHR data)

* 1 1 * b c d | open bus | PPPbcd0 | PPPbcd1 | PPPbcd0 | PPPbcd1 | NROM-128

1 0 1 * * * * | PPPbcda | PPP1100 | PPP1101 | PPP1110 | PPP1111 | $6000 + last 32 kB

Pal equations:

Code:

nREGWR = (!CPU_A14) | (!CPU_A13) | (!CPU_A12) | (CPU_nROMSEL) | (CPU_RnW);

PRG_nCE = (CPU_nROMSEL & !REG_A2) |

(CPU_nROMSEL & !REG_A0) |

(!CPU_A14 & CPU_nROMSEL) |

(!CPU_A13 & CPU_nROMSEL) |

(CPU_nROMSEL & REG_A1) |

(!CPU_RnW);

PRG_A13 = (CPU_A13 & !CPU_nROMSEL & !REG_A1) |

(CPU_A13 & !REG_A1 & !REG_A2) |

(REG_D7 & !REG_A0 & REG_A1) |

(CPU_nROMSEL & REG_D7 & REG_A0 & !REG_A1 & REG_A2) |

(CPU_A13 & REG_A0 & REG_A1) |

(CPU_A13 & !REG_A0 & !REG_A1);

PRG_A14 = (CPU_A14 & !REG_A0 & !REG_A1) |

(CPU_A14 & !CPU_nROMSEL & !REG_A1) |

(CPU_A14 & !REG_A1 & !REG_A2) |

(REG_D0 & REG_A1) |

(CPU_nROMSEL & REG_D0 & REG_A0) |

(REG_D0 & REG_A0 & !REG_A2);

PRG_A15 = (CPU_A14 & REG_A0 & !REG_A1 & !REG_A2) |

(!CPU_nROMSEL & REG_A0 & !REG_A1 & REG_A2) |

(REG_D1);

PRG_A16 = (CPU_A14 & REG_A0 & !REG_A1 & !REG_A2) |

(!CPU_nROMSEL & REG_A0 & !REG_A1 & REG_A2) |

(REG_D2);

PRG_nCE = (CPU_nROMSEL & !REG_A2) |

(CPU_nROMSEL & !REG_A0) |

(!CPU_A14 & CPU_nROMSEL) |

(!CPU_A13 & CPU_nROMSEL) |

(CPU_nROMSEL & REG_A1) |

(!CPU_RnW);

PRG_A13 = (CPU_A13 & !CPU_nROMSEL & !REG_A1) |

(CPU_A13 & !REG_A1 & !REG_A2) |

(REG_D7 & !REG_A0 & REG_A1) |

(CPU_nROMSEL & REG_D7 & REG_A0 & !REG_A1 & REG_A2) |

(CPU_A13 & REG_A0 & REG_A1) |

(CPU_A13 & !REG_A0 & !REG_A1);

PRG_A14 = (CPU_A14 & !REG_A0 & !REG_A1) |

(CPU_A14 & !CPU_nROMSEL & !REG_A1) |

(CPU_A14 & !REG_A1 & !REG_A2) |

(REG_D0 & REG_A1) |

(CPU_nROMSEL & REG_D0 & REG_A0) |

(REG_D0 & REG_A0 & !REG_A2);

PRG_A15 = (CPU_A14 & REG_A0 & !REG_A1 & !REG_A2) |

(!CPU_nROMSEL & REG_A0 & !REG_A1 & REG_A2) |

(REG_D1);

PRG_A16 = (CPU_A14 & REG_A0 & !REG_A1 & !REG_A2) |

(!CPU_nROMSEL & REG_A0 & !REG_A1 & REG_A2) |

(REG_D2);