I have dendy-clone which looks like that:

All games works (meaning - CPU works properly, CPU-PPU comunication also works) but there is some problem with video rendering - image looks just like internal VRAM would be broken (just some random mosaique with colors matching true colors - so Attribute Table probably is stored/read correctly).

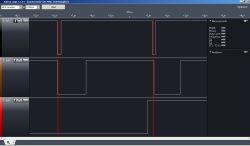

I disabled the internal PPU RAM and wired external RAM but no effect (thought VRAM is broken):

Then I measured some things and what I found is that:

-There is completely no signal on PPU-A7/PPU-A6

-Amplitude on PPU-A8/A5 is two times less than other signals - around 2V (on other pins around 4V)

I thought of any way of recover PPU-A7-PPU-A6. I watched PPU-D, but unfortunatelly those NES-on-CHIP clones does not produce lower 8 address bits on PPU-D prior latching A0-A7 (just like DIP-40 PPU in order to drive `373 external latch)

Any idea how to recover those missing signals? If not, I even thought of adding board with UA6538+VRAM+373 and some address decoder based on !ROMSEL, M2, A14 but:

1. How to clock the external UA6538 so that it uses the same clock as glob-top and no phase drift occurs? There is only external quartz in this NOC board, while all generating circuit is inside glob top.

2. How to wire the external PPU with NOC's CPU? -> `broken` PPU cannot be probably disconnected from NOC CPU, but what about putting TWO PPUs on the same bus at the same memory range (and maybe add some kind of buffer which will cut off second PPU's DATA bus from CPU on reads)

All games works (meaning - CPU works properly, CPU-PPU comunication also works) but there is some problem with video rendering - image looks just like internal VRAM would be broken (just some random mosaique with colors matching true colors - so Attribute Table probably is stored/read correctly).

I disabled the internal PPU RAM and wired external RAM but no effect (thought VRAM is broken):

Then I measured some things and what I found is that:

-There is completely no signal on PPU-A7/PPU-A6

-Amplitude on PPU-A8/A5 is two times less than other signals - around 2V (on other pins around 4V)

I thought of any way of recover PPU-A7-PPU-A6. I watched PPU-D, but unfortunatelly those NES-on-CHIP clones does not produce lower 8 address bits on PPU-D prior latching A0-A7 (just like DIP-40 PPU in order to drive `373 external latch)

Any idea how to recover those missing signals? If not, I even thought of adding board with UA6538+VRAM+373 and some address decoder based on !ROMSEL, M2, A14 but:

1. How to clock the external UA6538 so that it uses the same clock as glob-top and no phase drift occurs? There is only external quartz in this NOC board, while all generating circuit is inside glob top.

2. How to wire the external PPU with NOC's CPU? -> `broken` PPU cannot be probably disconnected from NOC CPU, but what about putting TWO PPUs on the same bus at the same memory range (and maybe add some kind of buffer which will cut off second PPU's DATA bus from CPU on reads)