Fisher wrote:

unindentified mapper

And pins 16-

1920 aren't connected to anything. Almost certainly cloned VRC2.

The two '191s and the '393 probably make up the IRQ source.

—

No obvious errors in the PRG or CHR dumps. They only differ from the Japanese release of the game by PRG:604 bytes and CHR:614 bytes.

CHR is, as typical, just blanking out the right

sholders' names:

Attachment:

Gremlin 2 - Shinshu Tanjou (J) - differences.gif [ 3.74 KiB | Viewed 3960 times ]

Gremlin 2 - Shinshu Tanjou (J) - differences.gif [ 3.74 KiB | Viewed 3960 times ]

—

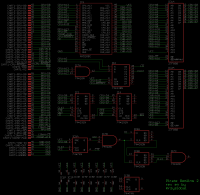

Now having traced the PCB:

* VRC2, but in the VRC4e pinout variant (addresses in order, 0/4/8/C)

* IRQ prescaler of ÷ 256

* Presettable up-counting IRQ, IRQ on overflow

* IRQ can be stopped and prescaler cleared, or running

Additional register map beyond VRC2:

mask $F00C,

$F000: load data bus to IRQ counters, no effect on prescaler

$F008: load D0 to IRQ enable(D0=1)/halt(D0=0)

If IRQ halted: prescaler ('393) is cleared (reset to 0). Counter is halted (/CountEnable is high). Counter is NOT cleared.

If IRQ enabled: prescaler counts up every M2 cycle

(on the falling edge). Loads take precedence over counting, if both would

(could?) happen at the same time.

Weird idiosyncrasies:

The '191s count on a

rising edge of their clock input, so the first time the '191s will count will be 128 M2 cycles after the counter is enabled. (And every 256 M2 cycles thereafter)

IRQs will self-acknowledge after 128 cycles, because the literal logic for IRQ being asserted is "counter = 0xFF and ClockInput=0"

1/3 of the 74'10 calculates NAND3(div256,div128,div32): it looks like there had been some effort to use a prescaler of ÷208 instead of 256, but nothing happens with the result of this calculationThe prescaler is

not affected by counter loads, so relative phase of the IRQ can be managed in way that won't care about IRQ latency.

Two worked examples:

* Stopping IRQ, loading counter with $FF, and then enabling IRQ will cause an immediate IRQ

* Stopping IRQ, loading counter with $FE, and then enabling IRQ will cause an IRQ in 256cy (Counter will increment in 128cy, and then ClockInput becomes 0 again in 256cy)

edit: grammar nits