Easy things first:

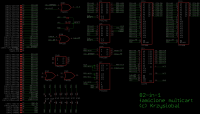

What you've traced shows this functionality:

Code:

+--------+++- not yet known

| |||

A~[1... ..up PPPP Puuu]

| |||| |

| ++++-+---- 32KB PRG slice (i.e. ROM A15 through A19)

+----------- very likely A20 = ROM1 vs ROM2

The remaining functions must exist in the remaining four bits:

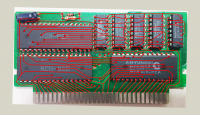

1- one bit must select between H/V nametable layout. This will be which of the pins on the two GD74LS174s connects to "pin 2" on the

74LS153.

2- one bit must disable writes to the HY6264 RAM. This will be which of the pins on the two GDLS174s connect to ... some of the pins on the 74LS32.

3- one bit must select between 16K and 32K PRG. This will be which of the pins on the two GD74LS174s connects to "pin 14" on the 74LS153.

4- one bit must select between the upper and lower half when in 16K PRG mode. This will be two of pins 3-6 on the 74LS153.

Either way, one of these two kazoo fragments should give you a valid dump:

Code:

board <- {

mappernum = 100, /* Note: No mapper yet assigned to this board. 100 is just a "known bad" value. */

cpu_rom = {

size_base = 16 * mega, size_max = 16 * mega, banksize = 0x8000

},

ppu_rom = {

size_base = 0, size_max = 0, banksize = 0

},

ppu_ramfind = false, vram_mirrorfind = true

};

function cpu_dump(d, pagesize, banksize) {

for (local i = 0; i < pagesize; i += 1) {

cpu_write(d, 0x8000|(i*8), i);

cpu_read(d, 0x8000, 0x4000);

cpu_read(d, 0xc000, 0x4000);

}

}

OR

Code:

// Same as above, but change the similar line to:

cpu_write(d, 0x8207|(i*8), i);