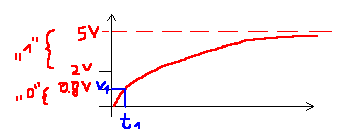

As we know when we use PRG /CE and M2 to decode $6000-$7FFF, but they are not change at the same time. PRG /CE is the logical NAND of M2 and PRG A15. This is accomplished by sending M2 and PRG A15 into a 74LS139 two-to-four line decoder on the NES main board. This introduces a small delay of up to 33 ns between the time M2 rises and the time PRG /CE rises.

If this delay is too long it can cause unintentional writes to PRG RAM when writing to mapper registers $E000-$FFFF.

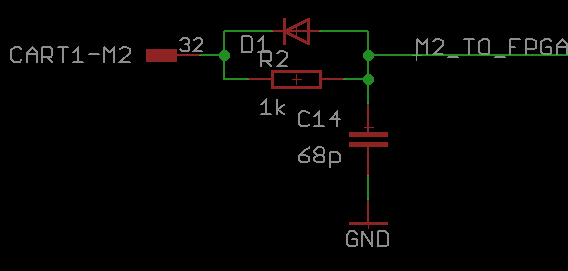

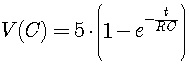

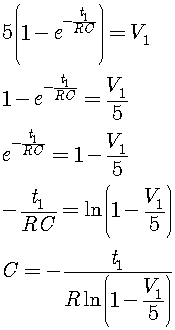

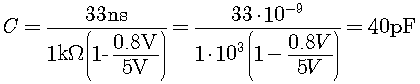

So in a cpld mappers, how to do this:(how to delay 33ns)

If this delay is too long it can cause unintentional writes to PRG RAM when writing to mapper registers $E000-$FFFF.

So in a cpld mappers, how to do this:(how to delay 33ns)

Code:

PRG RAM +CE = A13 AND A14 AND /ROMSEL AND delay(M2, 33 ns)