So here is a project that I've been working on.

It's a SNROM version of VegaPlay. With a 256KB flash you can load 7 non-banking NSFs <32K (you lose the vector table and trampoline bytes from each 32K 'slot'. One 32K 'slot' is used for reset code and CHR data that's banked out after reset.).

The runtime is loaded into WRAM during reset, leaving the PRG space for NSFs.The testing I've done so far: works with FamiTracker NSFs but can have strange behavior with other NSF Players. I use Nestopia so can't speak for other EMUs.

I've tried to simplify the loading and compiling process, you don't need to strip the header from the NSFs and there is a User Configure file to do all the editing in, so the main ASM file can be left alone.

Just drop all your NSFs into the build folder, edit User Configure with the NSF titles and load addresses and run the compile bat. It will spit out a .NES and/or a .PRG ready to flash.

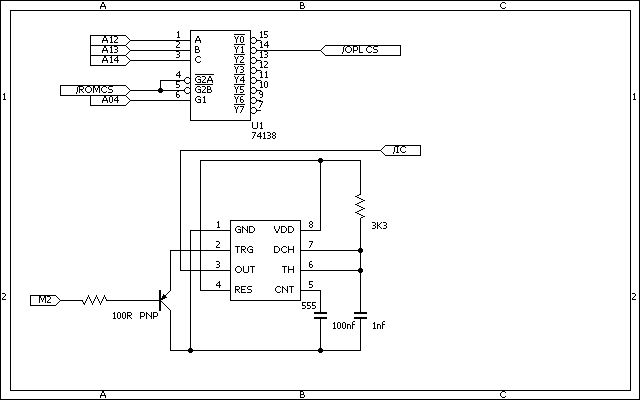

With a compiler switch you can use the normal playback timing based on the NMI or use Sync pulses on controller 2 (this is based on FamiSlayer v6.66 by Heavyw8bit). I'm working on a cheap (16F628 based) Midi Clock to NES Sync24 converter. Testing a proto board, so both the HW and the NES rom could change as things progress.

These preview ROMs are NSFs from the FamiMiniCompo10, the User Configure.asm has the title info.NSF 1, 3 and 4 have strange behavior, plays for a short time then triggers a bankswitch. Still testing

The Pad1 controls:

Up/Down - song # (all these are single song NSFs so trying to run a song other than the first will crash it)

Left/Right - cycle thru the 7 NSFs

Start Button - Start/Stop playback

UPDATE 7/20/2014:

Added a preview rom with a fixed Read routines. No more strange behavior, at least from the NES

https://www.dropbox.com/sh/g6osy6uozook ... -yjh_7WJUa

Yogi

It's a SNROM version of VegaPlay. With a 256KB flash you can load 7 non-banking NSFs <32K (you lose the vector table and trampoline bytes from each 32K 'slot'. One 32K 'slot' is used for reset code and CHR data that's banked out after reset.).

The runtime is loaded into WRAM during reset, leaving the PRG space for NSFs.

I've tried to simplify the loading and compiling process, you don't need to strip the header from the NSFs and there is a User Configure file to do all the editing in, so the main ASM file can be left alone.

Just drop all your NSFs into the build folder, edit User Configure with the NSF titles and load addresses and run the compile bat. It will spit out a .NES and/or a .PRG ready to flash.

With a compiler switch you can use the normal playback timing based on the NMI or use Sync pulses on controller 2 (this is based on FamiSlayer v6.66 by Heavyw8bit). I'm working on a cheap (16F628 based) Midi Clock to NES Sync24 converter. Testing a proto board, so both the HW and the NES rom could change as things progress.

These preview ROMs are NSFs from the FamiMiniCompo10, the User Configure.asm has the title info.

The Pad1 controls:

Up/Down - song # (all these are single song NSFs so trying to run a song other than the first will crash it)

Left/Right - cycle thru the 7 NSFs

Start Button - Start/Stop playback

UPDATE 7/20/2014:

Added a preview rom with a fixed Read routines. No more strange behavior, at least from the NES

https://www.dropbox.com/sh/g6osy6uozook ... -yjh_7WJUa

Yogi