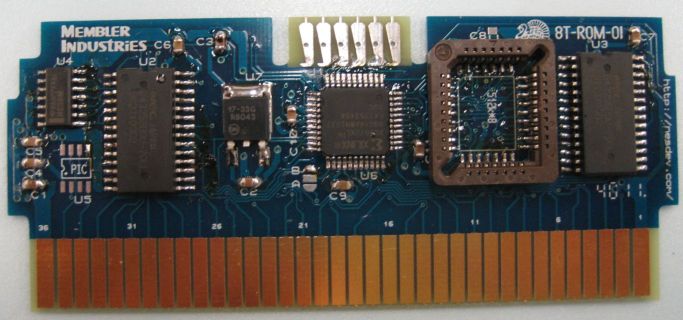

You can call it "eight tee" or "infinite turkeys", something like that.

Not for sale yet.. this is just the prototype and I'm about to put it through a lot of tests.

I got the boards this week and have soldered this one, built the JTAG cable for writing the CPLD (verified), currently I'm writing a full test program so I can verify if it works. Once that is settled, if I don't need to redo the board, next step will be releasing a PowerPak mapper file. Once there are enough demos/test ROMs, then emulator support should be possible.

For larger images, see here:

http://membler-industries.com/memblers/pics/IMG_2089.jpg

http://membler-industries.com/memblers/pics/IMG_2091.jpg

http://membler-industries.com/memblers/pics/IMG_2092.jpg

There is a CPLD, but this is not a universal type of board. It's not a clone of any mapper, but I'd say it is most similar to MMC2 and MMC4 because there are PPU 'interrupt' tiles that can be used to automate CHR banking at nametable grid (BG) or scanline (sprite) precision.

Basic mapper specs:

Stuff that remains to be implemented, but should be do-able (not all at once though):

To accompany this cartridge, I'm working on some communications software that will provide various functions, most importantly loading ROMs. I talked with blargg about his bootloader and I think we both came up with some pretty cool ideas.

Because of that, the USB adapter I'll build may have any (hopefully all) these features (I'll make another thread for this later):

So yeah, the PLCC socket is just for testing, pretty soon I'll try to make a kazzo script so I can solder a blank chip on, then write a bootloader onto it.

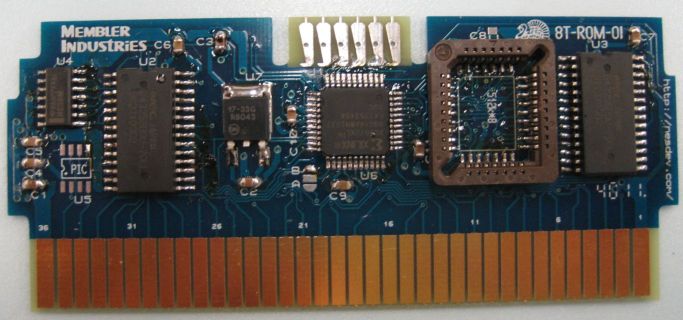

Not for sale yet.. this is just the prototype and I'm about to put it through a lot of tests.

I got the boards this week and have soldered this one, built the JTAG cable for writing the CPLD (verified), currently I'm writing a full test program so I can verify if it works. Once that is settled, if I don't need to redo the board, next step will be releasing a PowerPak mapper file. Once there are enough demos/test ROMs, then emulator support should be possible.

For larger images, see here:

http://membler-industries.com/memblers/pics/IMG_2089.jpg

http://membler-industries.com/memblers/pics/IMG_2091.jpg

http://membler-industries.com/memblers/pics/IMG_2092.jpg

There is a CPLD, but this is not a universal type of board. It's not a clone of any mapper, but I'd say it is most similar to MMC2 and MMC4 because there are PPU 'interrupt' tiles that can be used to automate CHR banking at nametable grid (BG) or scanline (sprite) precision.

Basic mapper specs:

- 512kB PRG-ROM - 16kB PRG page size (either can fixed, or both paged, 32kB mode also possible). Flash memory - 4kB sectors.

- 32kB CHR-RAM - 1kB CHR page (smaller CPLD can use 2 * 2kB paged, 2 * 2kb fixed)

- 32kB WRAM - 8kB page size

- 8 control registers at $5000 - $5038 - 4 bits wide

- NES Expansion port enable - creates 4 8-bit ports, NES can read or write to an expansion port device at $5038,$5039,$503A,$503B - for use with future synthesizer, network adapter, ?? (this requires front-loader NES though). Unfortunately, enabling this feature requires changing jumpers on the board and different firmware.

- Automated CHR bankswitching, also a CPU IRQ function (that comes with some side-effects, though)

- H/V/single0/single1 mirroring control register

Stuff that remains to be implemented, but should be do-able (not all at once though):

- 8 * 1kB CHR banking

- CPU cycle timer

- 4-screen mirroring, nametable bankswitching (either one requires changing jumper on the board)

To accompany this cartridge, I'm working on some communications software that will provide various functions, most importantly loading ROMs. I talked with blargg about his bootloader and I think we both came up with some pretty cool ideas.

Because of that, the USB adapter I'll build may have any (hopefully all) these features (I'll make another thread for this later):

- NES controller port to USB

- hardware flow control mode

- software flow control mode

- external reset - it needs NMI and/or IRQ/BRK activity, will fail if NES CPU is locked up - reduces need to manually reset NES during testing

- plus various software-based features (supported in Windows, should be portable to OSX and Linux) - so far only the serial communication is platform dependent.

So yeah, the PLCC socket is just for testing, pretty soon I'll try to make a kazzo script so I can solder a blank chip on, then write a bootloader onto it.