About MMC3 in puNES:

I'd like to know your MMC3 IRQ implementation, since it passes through all the tests. I want to know about PPU A12 rising:

a) how do you threat A12 for sprites 8x16? FCEUX doesn't clock the IRQ if PPU $2000 AND $38 != $18.

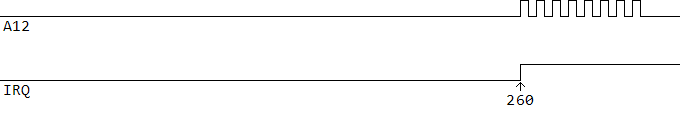

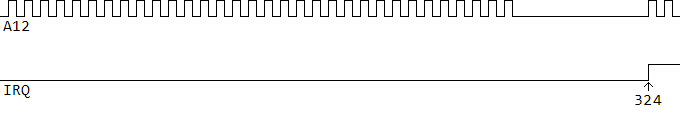

b) how do you handle the IRQ for the cycle 324, regarding the previous scanline? (assuming no timestamp system)

c) do you clock the IRQ at PPU cycle 260 with A12 high, if BG=$0000 and SP=$1000? (read a) again)

My old code fails for the scanline timing test, "scanline 0 IRQ should occur later/sooner when $2000:$08".

Mind you to give me an hand?

I'd like to know your MMC3 IRQ implementation, since it passes through all the tests. I want to know about PPU A12 rising:

a) how do you threat A12 for sprites 8x16? FCEUX doesn't clock the IRQ if PPU $2000 AND $38 != $18.

b) how do you handle the IRQ for the cycle 324, regarding the previous scanline? (assuming no timestamp system)

c) do you clock the IRQ at PPU cycle 260 with A12 high, if BG=$0000 and SP=$1000? (read a) again)

My old code fails for the scanline timing test, "scanline 0 IRQ should occur later/sooner when $2000:$08".

Mind you to give me an hand?