sorry for all the threads in a short time. didn't want to throw this in the unrelated APU thread.

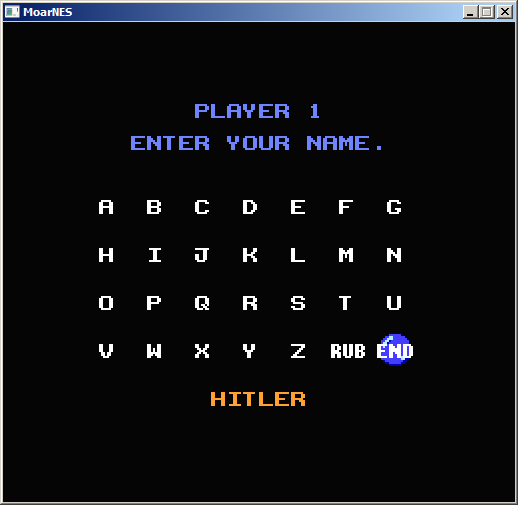

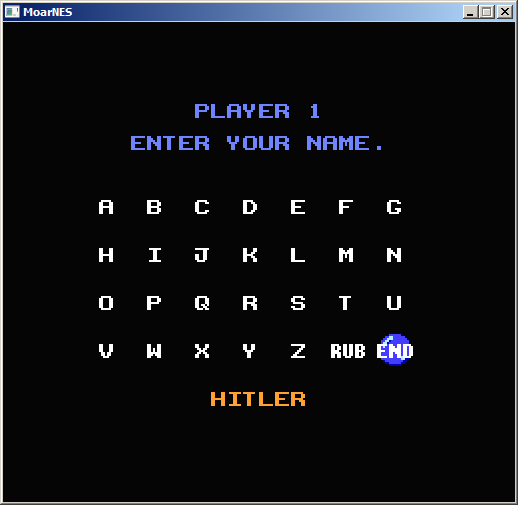

when i play Marble Madness and Battletoads in my emulator, they both have a similar problem. in MM, the background seems to revert to a scroll value of zero 3/4 of the way down the screen. sprites are also not being shown below this point. other than this, it seems to play okay.

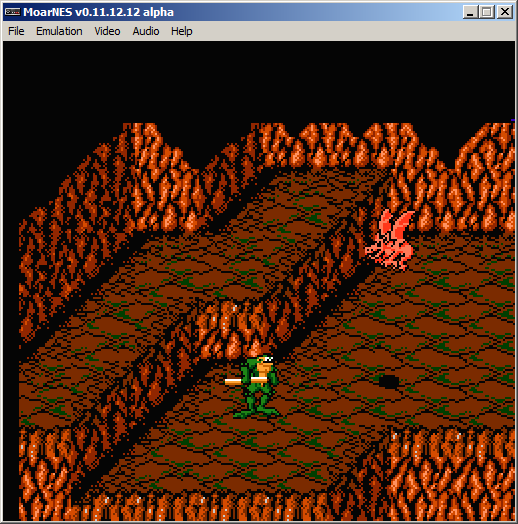

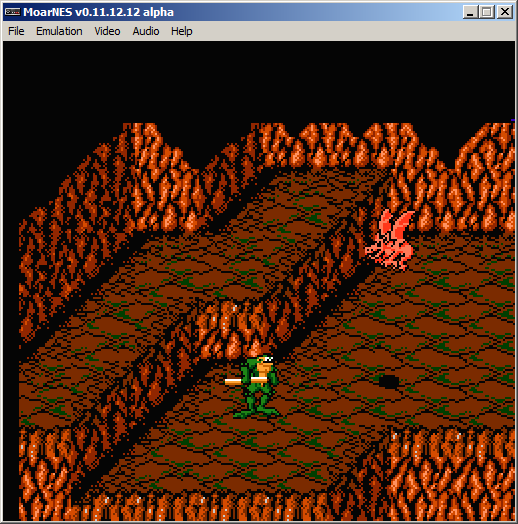

in BT, sprites all show just fine everywhere but the background starts too low at the top of the frame and then wraps around. i have a feeling they're both PPU frame timing. in blargg's VBL basics rom i fail with "VBL period is way off" but from what i know, i thought i was doing it right and am not sure where to go from here. might be some stupid oversight. probably is.

this is the meat of my main frame loop. it passes the VBL clear flag tests after tonight. i did some fiddling with it moving the clear point around inside of scanline 261.

and this is the renderscanline function:

i have not run into any issues remotely like this in any other games. in fact, everything else i run plays more or less flawlessly. (with a small handful of exceptions)

one other thing that kind of bugs me is the status bar in SMB1 tends to flicker often. not sure if it's related.

oh and for the life of me i CANNOT figure out why i fail blargg's NMI control test ROM with "Should occur when enabled and VBL begins"

........ because it certainly looks to me like it occurs when enabled and VBL begins, unless it's saying that because of some other prerequisite the test relies on but doesnt check for isn't being met? am i beginning vblank in the wrong place?

when i play Marble Madness and Battletoads in my emulator, they both have a similar problem. in MM, the background seems to revert to a scroll value of zero 3/4 of the way down the screen. sprites are also not being shown below this point. other than this, it seems to play okay.

in BT, sprites all show just fine everywhere but the background starts too low at the top of the frame and then wraps around. i have a feeling they're both PPU frame timing. in blargg's VBL basics rom i fail with "VBL period is way off" but from what i know, i thought i was doing it right and am not sure where to go from here. might be some stupid oversight. probably is.

this is the meat of my main frame loop. it passes the VBL clear flag tests after tonight. i did some fiddling with it moving the clear point around inside of scanline 261.

Code:

memcpy(&SpriteBuffer[0], &SpriteRAM[0], 256);

savedhscroll = hscroll; savedvscroll = vscroll;

for (scanline=0; scanline<240; scanline++) {

renderscanline(scanline); exec6502(28);

totalscanlines++;

}

PPUdata.vblank = 1;

if (PPUdata.nmivblank) nmi6502();

for (scanline=240; scanline<261; scanline++) {

exec6502(113);

totalscanlines++;

}

exec6502(70);

PPUdata.vblank = 0;

PPUdata.spr0hit = 0;

if (totalframes&1) exec6502(44); else exec6502(43);

savedhscroll = hscroll; savedvscroll = vscroll;

for (scanline=0; scanline<240; scanline++) {

renderscanline(scanline); exec6502(28);

totalscanlines++;

}

PPUdata.vblank = 1;

if (PPUdata.nmivblank) nmi6502();

for (scanline=240; scanline<261; scanline++) {

exec6502(113);

totalscanlines++;

}

exec6502(70);

PPUdata.vblank = 0;

PPUdata.spr0hit = 0;

if (totalframes&1) exec6502(44); else exec6502(43);

and this is the renderscanline function:

Code:

void renderscanline(WORD scanline) {

WORD tmpx;

for (tmpx=0; tmpx<256; tmpx++) { sprback[tmpx] = 0; backgnd[tmpx] = 0; sprfront[tmpx] = 0; spr0collide[tmpx] = 0; }

if (PPUdata.sprvisible) drawsprites(scanline, 1);

if (PPUdata.bgvisible) drawbackground(scanline);

if (PPUdata.sprvisible) drawsprites(scanline, 0);

for (tmpx=0; tmpx<256; tmpx++) {

if (tmpx==hit0x && scanline==hit0y) PPUdata.spr0hit = 1;

if ((tmpx%3)==0) exec6502(1);

if (sprback[tmpx]==0) outputNES[scanline][tmpx] = PPUread(0x3F00);

else outputNES[scanline][tmpx] = PPUread(sprback[tmpx]);

if (backgnd[tmpx]>0) {

outputNES[scanline][tmpx] = PPUread(backgnd[tmpx]);

if (spr0collide[tmpx]==1 && tmpx<255) { hit0x = tmpx; hit0y = scanline+1; }

}

if (sprfront[tmpx]>0) outputNES[scanline][tmpx] = PPUread(sprfront[tmpx]);

}

}

WORD tmpx;

for (tmpx=0; tmpx<256; tmpx++) { sprback[tmpx] = 0; backgnd[tmpx] = 0; sprfront[tmpx] = 0; spr0collide[tmpx] = 0; }

if (PPUdata.sprvisible) drawsprites(scanline, 1);

if (PPUdata.bgvisible) drawbackground(scanline);

if (PPUdata.sprvisible) drawsprites(scanline, 0);

for (tmpx=0; tmpx<256; tmpx++) {

if (tmpx==hit0x && scanline==hit0y) PPUdata.spr0hit = 1;

if ((tmpx%3)==0) exec6502(1);

if (sprback[tmpx]==0) outputNES[scanline][tmpx] = PPUread(0x3F00);

else outputNES[scanline][tmpx] = PPUread(sprback[tmpx]);

if (backgnd[tmpx]>0) {

outputNES[scanline][tmpx] = PPUread(backgnd[tmpx]);

if (spr0collide[tmpx]==1 && tmpx<255) { hit0x = tmpx; hit0y = scanline+1; }

}

if (sprfront[tmpx]>0) outputNES[scanline][tmpx] = PPUread(sprfront[tmpx]);

}

}

i have not run into any issues remotely like this in any other games. in fact, everything else i run plays more or less flawlessly. (with a small handful of exceptions)

one other thing that kind of bugs me is the status bar in SMB1 tends to flicker often. not sure if it's related.

oh and for the life of me i CANNOT figure out why i fail blargg's NMI control test ROM with "Should occur when enabled and VBL begins"

........ because it certainly looks to me like it occurs when enabled and VBL begins, unless it's saying that because of some other prerequisite the test relies on but doesnt check for isn't being met? am i beginning vblank in the wrong place?