Splitting from a discussion that came up in another unrelated thread ...

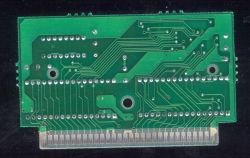

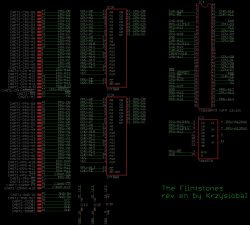

Mapper 48's IRQ is stated as being generated later than on the MMC3, but there is more: It seems impossible to get the IRQs to fire at the correct scanline in both The Jetsons: Cogswell's Caper's title screen and The Flintstones: The Rescue of Dino&Hoppy's status bar, either one will be off by one. The wiki page advises to XOR the latch value with FF to get the MMC3 equivalent value, which indicates that Taito's chip counts up, not down. When counting up, there is always the question of raising the IRQ when the counter reaches $FF (similar to the Namco 163's CPU Cycle counter) or when it wraps from $FF to $00. I noticed that Flintstones works well when raising the IRQ at counter $FF, while Jetsons works well when raising the IRQ at the time that the counter wraps (plus a delay of at least six CPU cycles, not four as the wiki states). This may be a coincidence, but it is the sort of thing that one would expect from a chip revision. If this hypothesis could be tested with the chips found in cartridges of both games, and confirmed, then a submapper could be allocated to indicate the IRQ counter behavior.

Mapper 48's IRQ is stated as being generated later than on the MMC3, but there is more: It seems impossible to get the IRQs to fire at the correct scanline in both The Jetsons: Cogswell's Caper's title screen and The Flintstones: The Rescue of Dino&Hoppy's status bar, either one will be off by one. The wiki page advises to XOR the latch value with FF to get the MMC3 equivalent value, which indicates that Taito's chip counts up, not down. When counting up, there is always the question of raising the IRQ when the counter reaches $FF (similar to the Namco 163's CPU Cycle counter) or when it wraps from $FF to $00. I noticed that Flintstones works well when raising the IRQ at counter $FF, while Jetsons works well when raising the IRQ at the time that the counter wraps (plus a delay of at least six CPU cycles, not four as the wiki states). This may be a coincidence, but it is the sort of thing that one would expect from a chip revision. If this hypothesis could be tested with the chips found in cartridges of both games, and confirmed, then a submapper could be allocated to indicate the IRQ counter behavior.