I'm not quite sure what you mean by VRAM read/writes delays, so I'll go ahead and assume I haven't implemented any. I haven't looked at Nintendulator's source in a long time, either..

I played a bit with the Visual NES, this might not be 100% accurate (especially since I did this in like 15 minutes), but nonetheless:

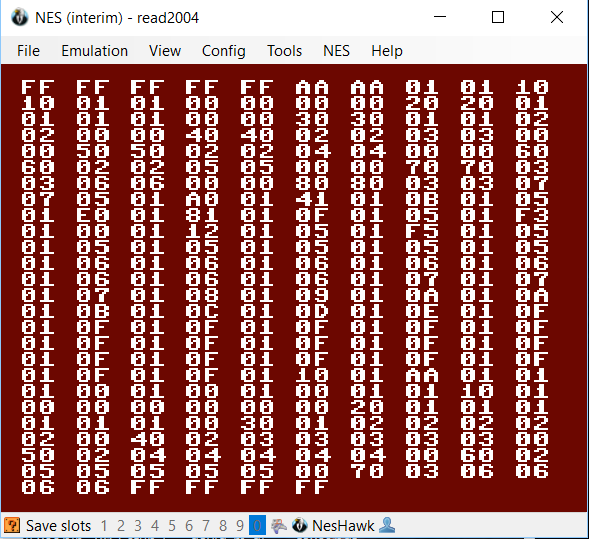

Code:

0A7960,55,F1,0819,19,18,FF,00,DF,2001,00,01,01,00, ;PPU rendering is disabled (01 in before-last column)

0A7961,55,F1,0819,19,18,FF,00,18,2001,00,00,01,00, ;CPU starts writing $18 to $2001, which will enable rendering

0A7961,56,F1,0819,19,18,FF,00,18,2001,00,00,01,00, ;PPU Cycle transitions from 85 to 86 ($55 -> $56)

0A7962,56,F1,0819,19,18,FF,00,18,2001,00,00,01,00,

0A7962,56,F1,0819,19,18,FF,00,18,2001,00,00,01,00,

0A7963,56,F1,0819,19,18,FF,00,18,2001,00,00,01,00,

0A7963,56,F1,0819,19,18,FF,00,18,2001,00,00,01,00,

0A7964,56,F1,0819,19,18,FF,00,18,2001,00,00,01,00,

0A7964,56,F1,0819,19,18,FF,00,18,2001,00,00,01,00,

0A7965,56,F1,0819,19,18,FF,00,18,2001,00,00,01,00,

0A7965,57,F1,0819,19,18,FF,00,18,2001,00,00,01,00, ;PPU cycle transition from 86->87 ($56 -> $57)

0A7966,57,F1,0819,19,18,FF,00,18,2001,00,00,01,00,

0A7966,57,F1,0819,19,18,FF,00,18,2001,00,01,00,01 ;Rendering is enabled (before-last column turns to 00), 1.5ish PPU cycles after the write

So there are 12 master clocks (1.5 ppu clocks) between the start of the write & the rendering flag being enabled.

This assumes I'm tracing the right signals, obviously - but it is called "rendering_disabled", so it's a pretty good bet.

Again, though, testing with Visual NES is not enough to prove anything, would need a test rom of sorts (but I do not have the slightest clue how one could test this, so I'm definitely not going to be the one writing a test for it :p)