Here's the results of my analysis of RAMBO-1 IRQ timing.

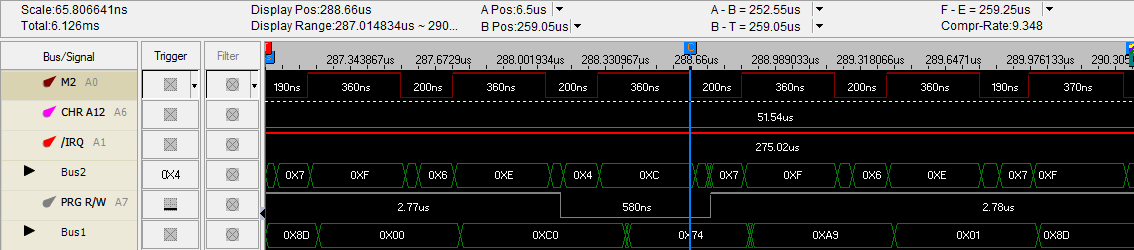

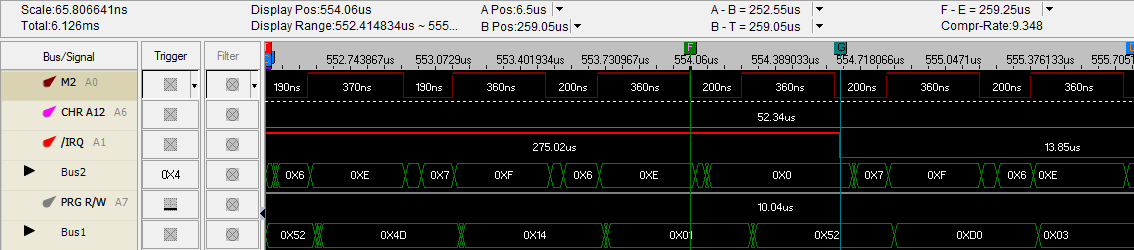

For MMC3-style IRQs, RAMBO-1 checks A12 on falling edges of M2. When it's time to do so, IRQ is asserted on the next falling edge of M2 (plus about 20ns). Since there are 4 possible CPU/PPU alignments, there are 4 variations of IRQ timing. Furthermore, since odd frames are 1 PPU cycle short, there are two different delays for each variation. Here's the IRQ assertion time, relative to the rising edge of A12, for each alignment:

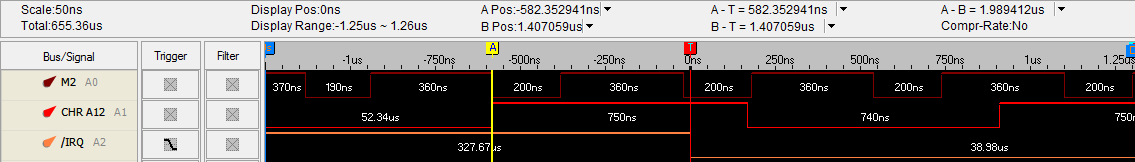

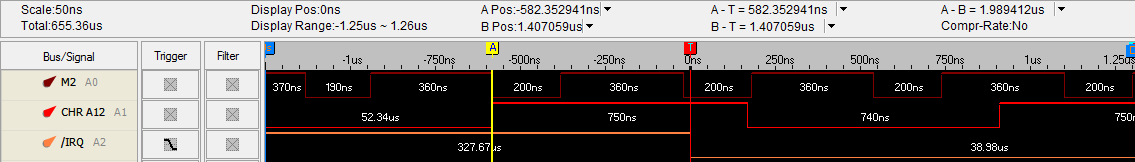

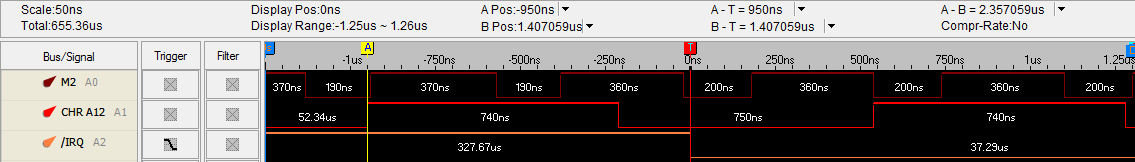

Alignment 1:

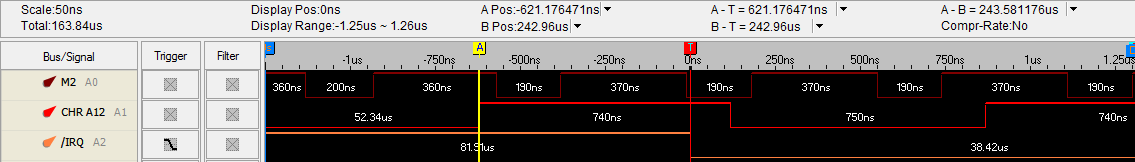

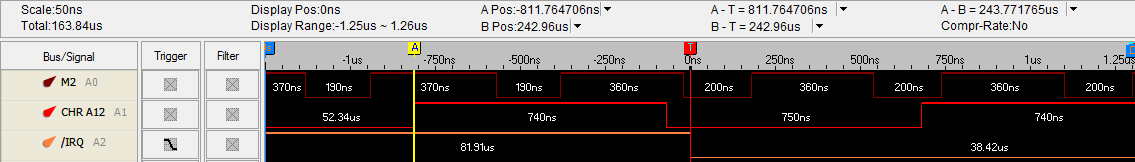

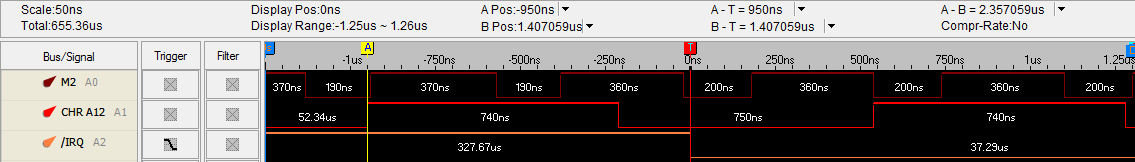

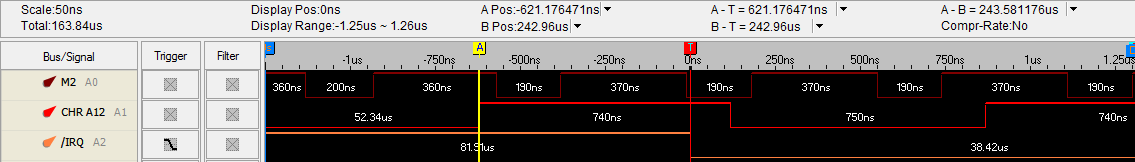

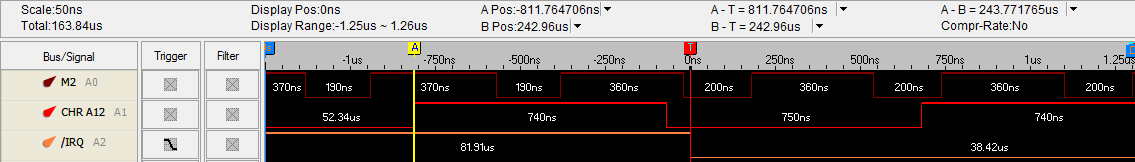

Alignment 2:

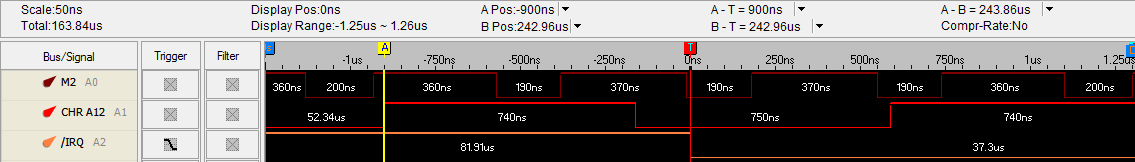

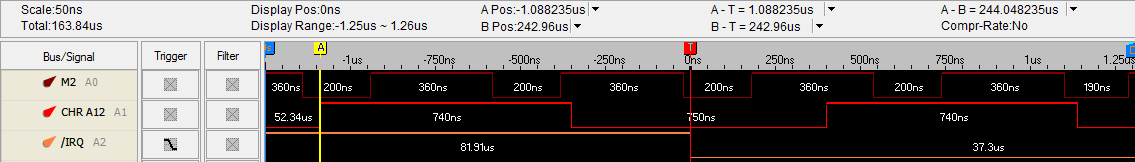

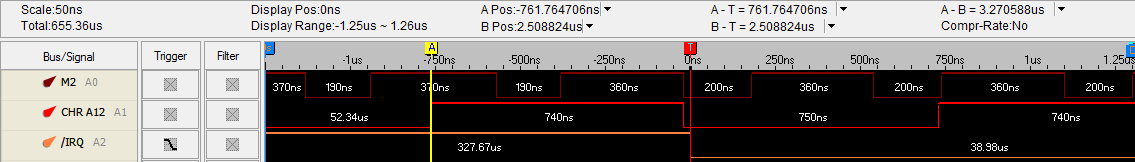

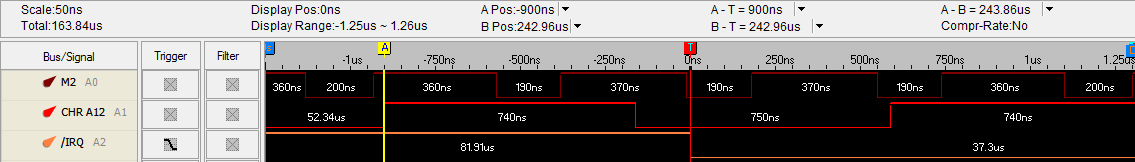

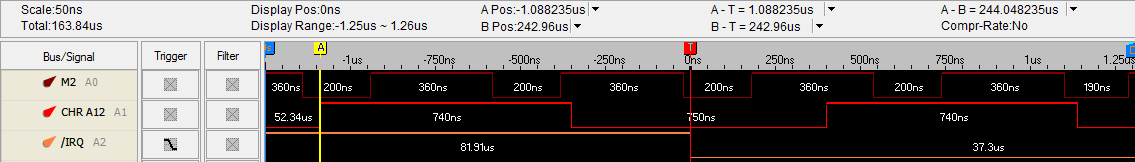

Alignment 3:

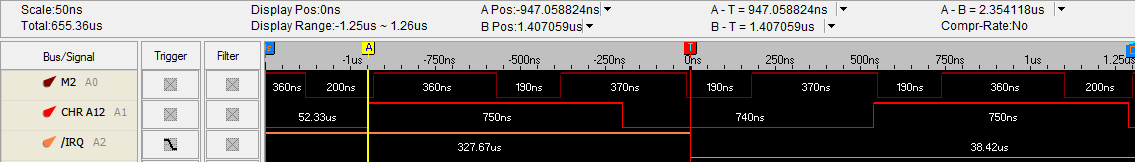

Alignment 4:

Edit: Revised CPU cycle-based IRQ info below.

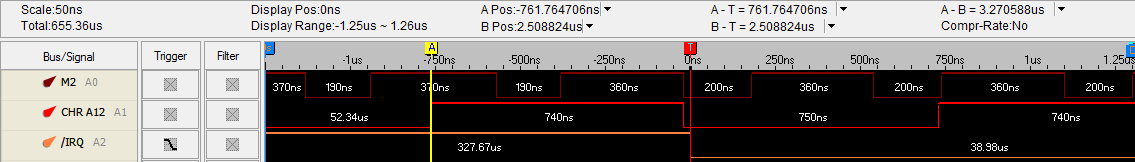

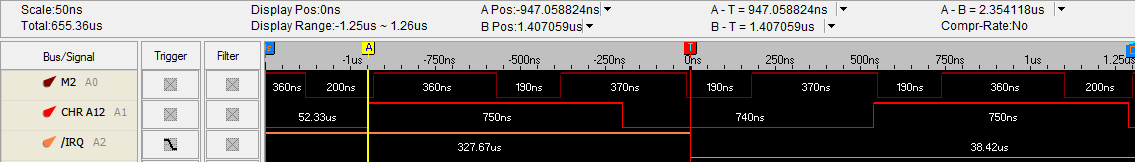

For MMC3-style IRQs, RAMBO-1 checks A12 on falling edges of M2. When it's time to do so, IRQ is asserted on the next falling edge of M2 (plus about 20ns). Since there are 4 possible CPU/PPU alignments, there are 4 variations of IRQ timing. Furthermore, since odd frames are 1 PPU cycle short, there are two different delays for each variation. Here's the IRQ assertion time, relative to the rising edge of A12, for each alignment:

Code:

Short Long

ns (cycles)

761 (4.1) 947 (5.1)

621 (3.3) 812 (4.3)

900 (4.8) 1088 (5.8)

582 (3.1) 950 (5.1)

ns (cycles)

761 (4.1) 947 (5.1)

621 (3.3) 812 (4.3)

900 (4.8) 1088 (5.8)

582 (3.1) 950 (5.1)

Alignment 1:

Alignment 2:

Alignment 3:

Alignment 4:

Edit: Revised CPU cycle-based IRQ info below.